### Short Course On Phase-Locked Loops IEEE Circuit and System Society, San Diego, CA

### **Digital Frequency Synthesizers**

Michael H. Perrott September 16, 2009

Copyright © 2009 by Michael H. Perrott All rights reserved.

# Why Are Digital Phase-Locked Loops Interesting?

- Performance is important

- Phase noise can limit wireless transceiver performance

- Jitter can be a problem for digital processors

- The standard analog PLL implementation is problematic in many applications

- Analog building blocks on a mostly digital chip pose design and verification challenges

- The cost of implementation is becoming too high ...

Can digital phase-locked loops offer excellent performance with a lower cost of implementation?

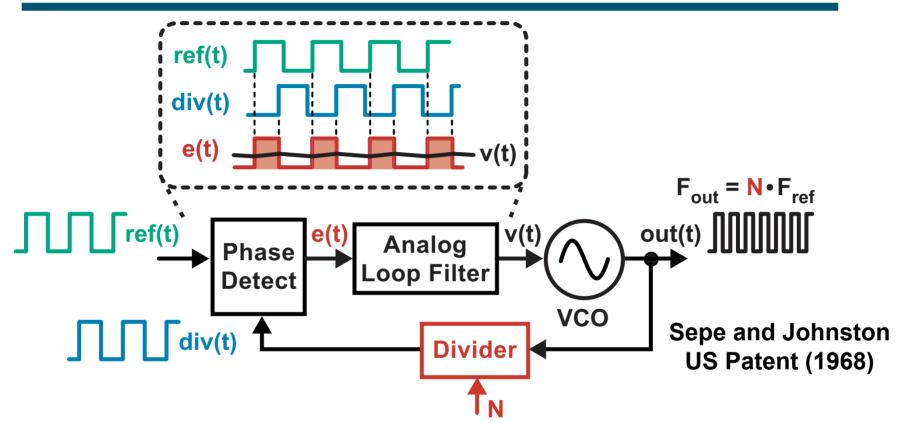

# Integer-N Frequency Synthesizers

- Use digital counter structure to divide VCO frequency

- Constraint: must divide by integer values

- Use PLL to synchronize reference and divider output

### **Tradeoff: Resolution vs PLL Bandwidth**

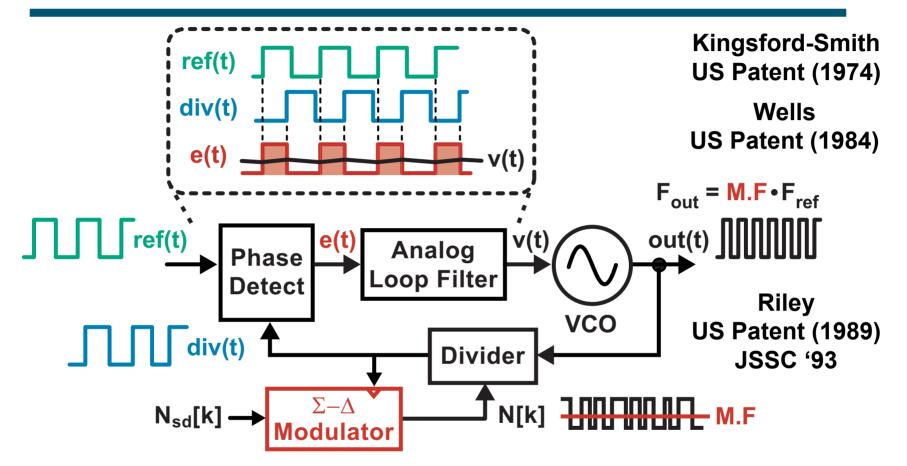

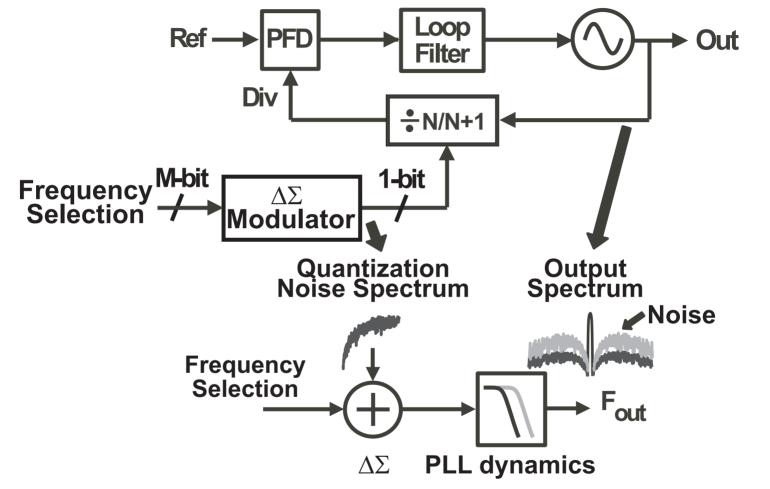

## Fractional-N Frequency Synthesizers

Dither divide value to achieve fractional divide values

PLL loop filter smooths the resulting variations

#### Tradeoff: Noise versus PLL Bandwidth

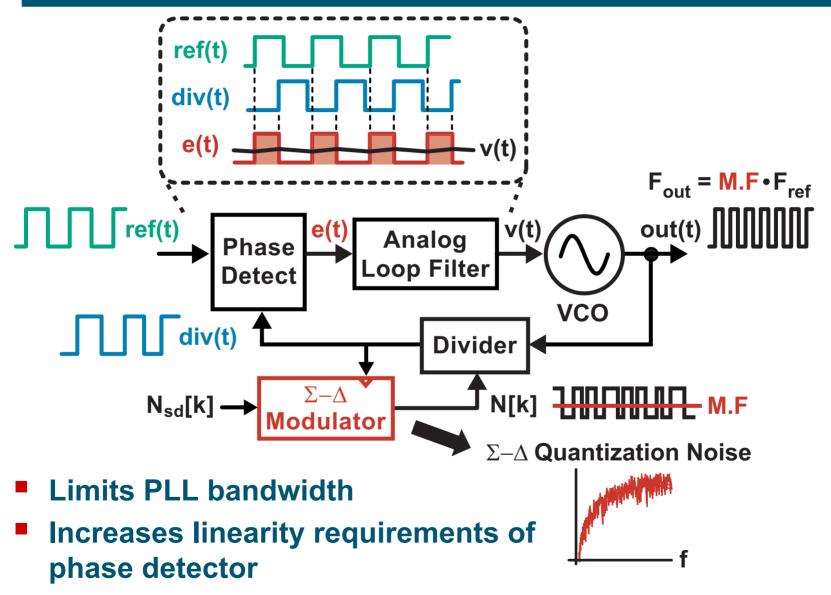

### The Issue of Quantization Noise

### Striving for a Better PLL Implementation

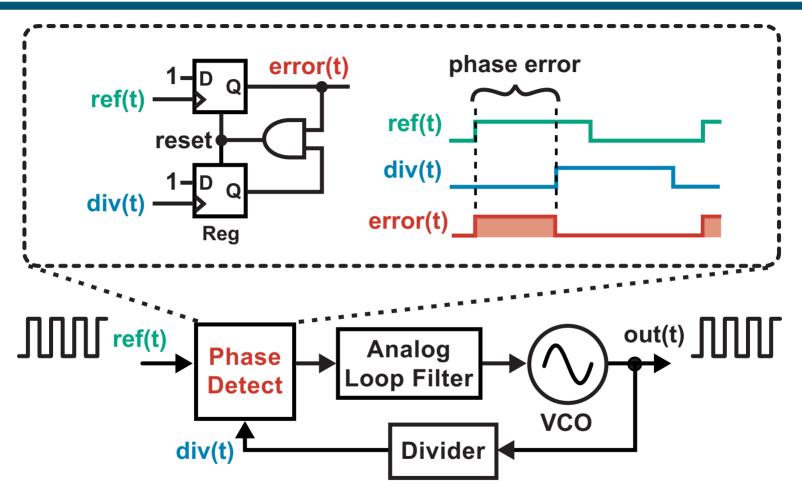

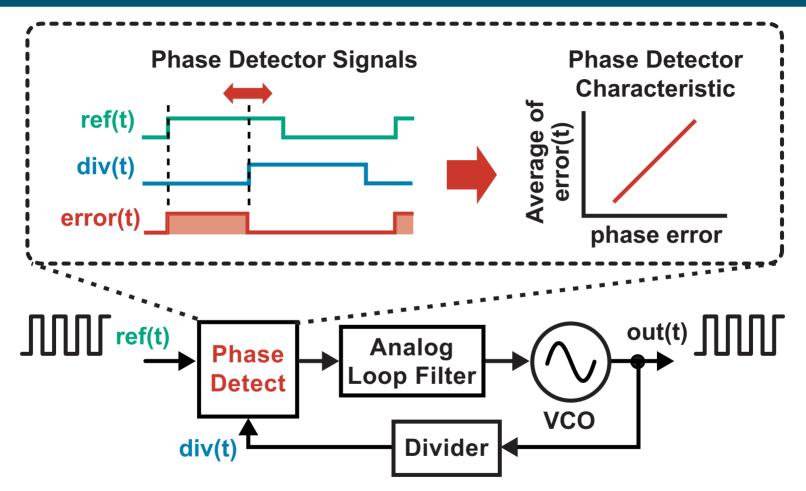

# **Analog Phase Detection**

Pulse width is formed according to phase difference between two signals

Average of pulsed waveform is applied to VCO input M.H. Perrott

# **Tradeoffs of Analog Approach**

Benefit: average of pulsed output is a continuous, linear function of phase error

Issue: analog loop filter implementation is undesirable M.H. Perrott

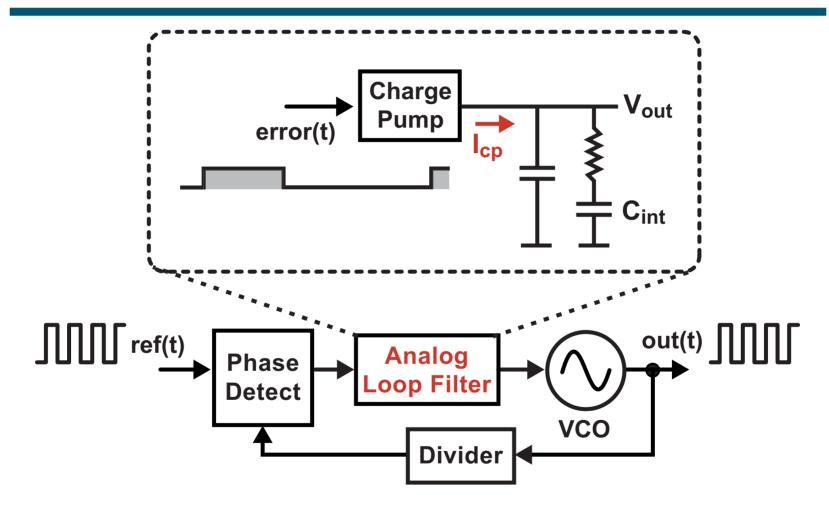

# **Issues with Analog Loop Filter**

- Charge pump: output resistance, mismatch

- Filter caps: leakage current, large area

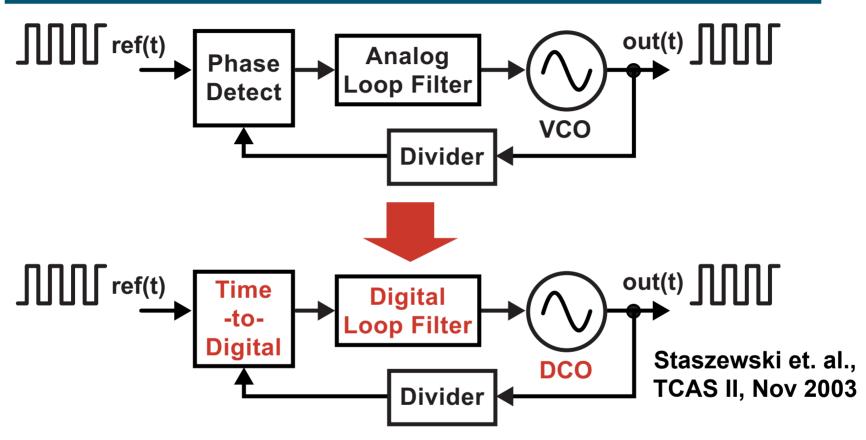

# Going Digital ...

- Digital loop filter: compact area, insensitive to leakage

- Challenges:

- Time-to-Digital Converter (TDC)

- Digitally-Controlled Oscillator (DCO)

### **Outline of Talk**

- Overview of Key Blocks (TDC and DCO)

- Modeling & CAD Tools

- High Performance TDC design

- Quantization Noise Cancellation

- DCO based on an efficient passive DAC structure

- Divider Design

- Loop Filter Design

- Prototype with measured Results

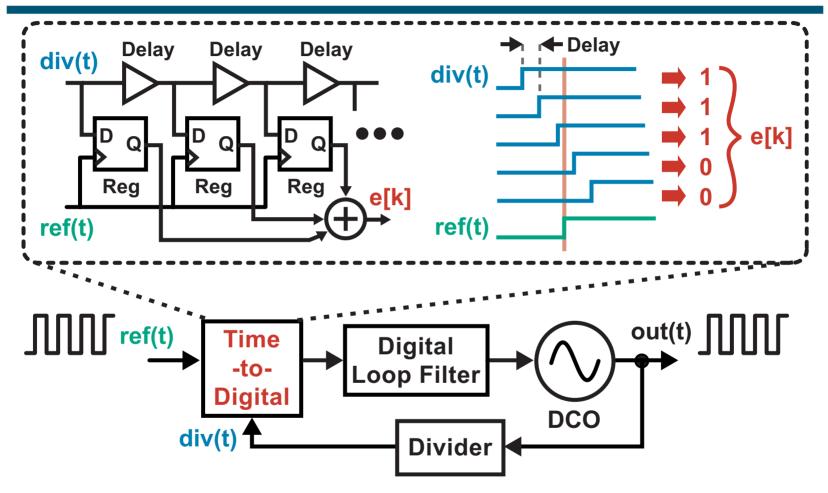

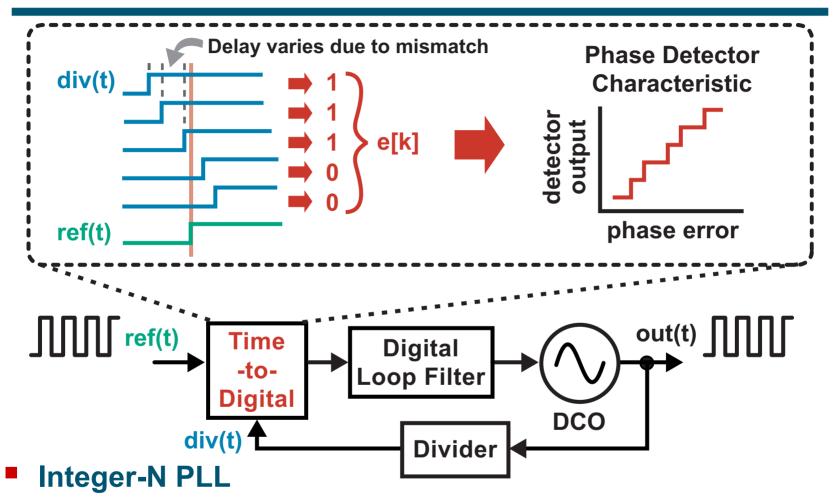

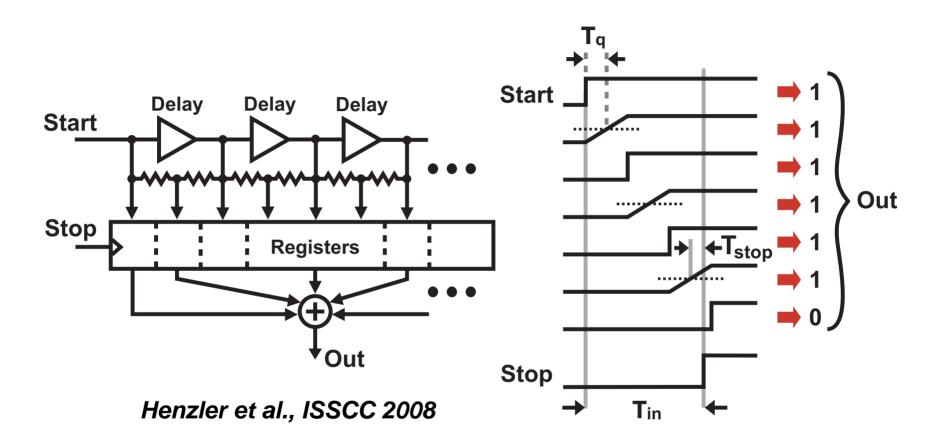

### **Classical Time-to-Digital Converter**

- Resolution set by a "Single Delay Chain" structure

- Phase error is measured with delays and registers

- Corresponds to a flash architecture

# Impact of Limited Resolution and Delay Mismatch

Limit cycles due to limited resolution (unless high ref noise)

Fractional-N PLL

**M.H.** Perrott Fractional spurs due to non-linearity from delay mismatch

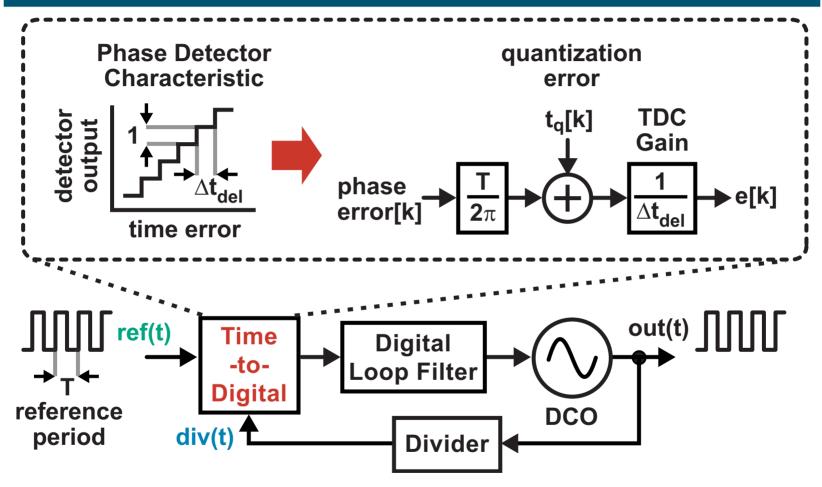

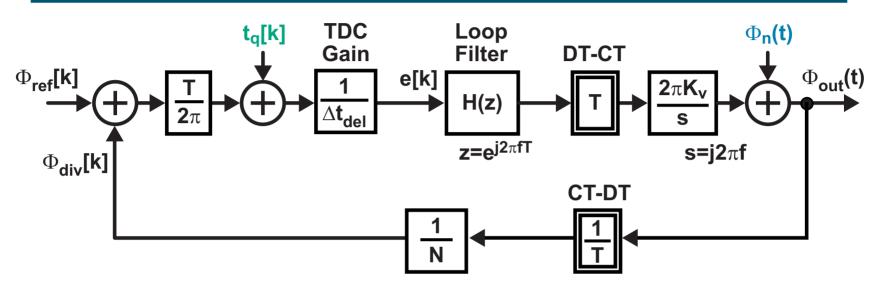

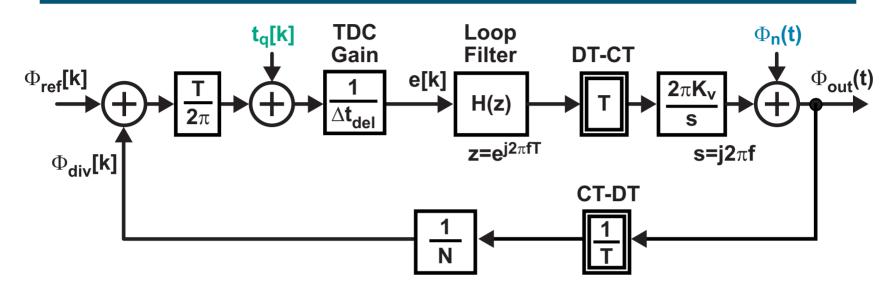

# Modeling of TDC

- Phase error converted to time error by scale factor:  $T/2\pi$

- TDC introduces quantization error: t<sub>a</sub>[k]

**TDC** gain set by average delay per step:  $\Delta t_{del}$

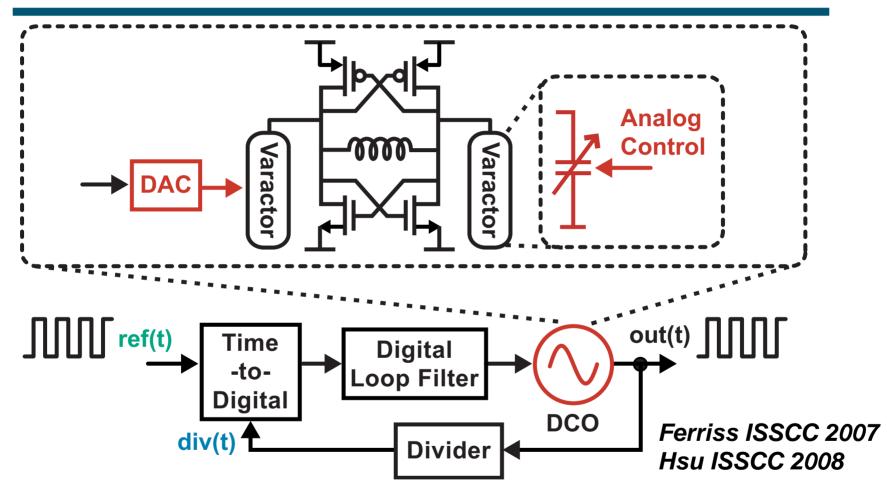

# A Straightforward Approach for Achieving a DCO

- Use a DAC to control a conventional LC oscillator

- Allows the use of an existing VCO within a digital PLL

Can be applied across a broad range of IC processes

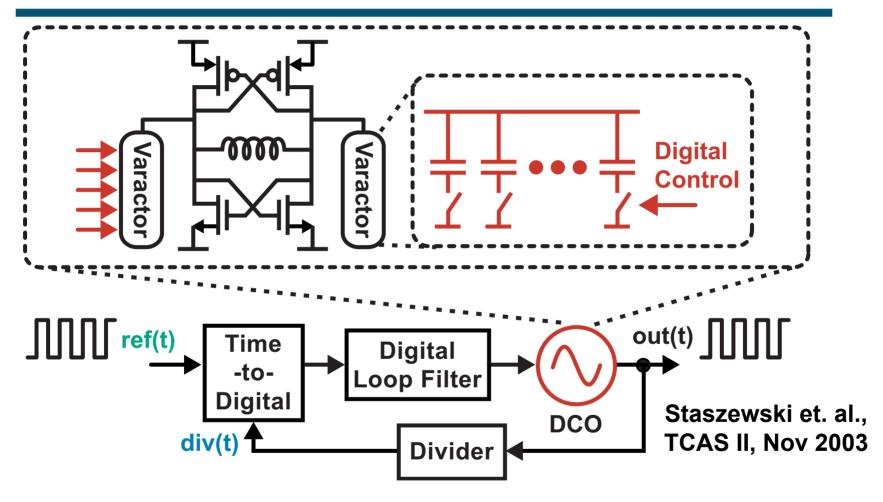

# A Much More Digital Implementation

Adjust frequency in an LC oscillator by switching in a variable number of small capacitors

Most effective for CMOS processes of 0.13u and below

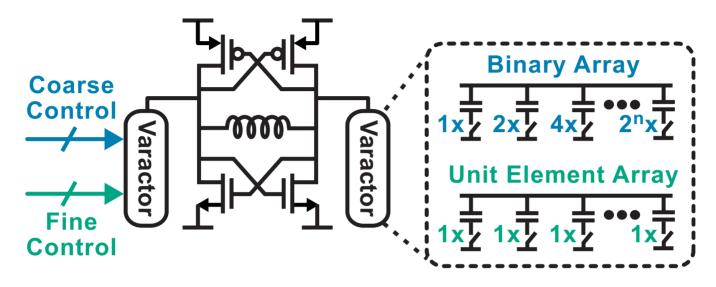

# Leveraging Segmentation in Switched Capacitor DCO

- Similar in design as *segmented* capacitor DAC structures

- Binary array: efficient control, but may lack monotonicity

- Unit element array: monotonic, but complex control

- Coarse and fine control segmentation of DCO

- Coarse control: active only during initial frequency tuning (leverage binary array)

- Fine control: controlled by PLL feedback (leverage unit element array to guarantee monotonicity)

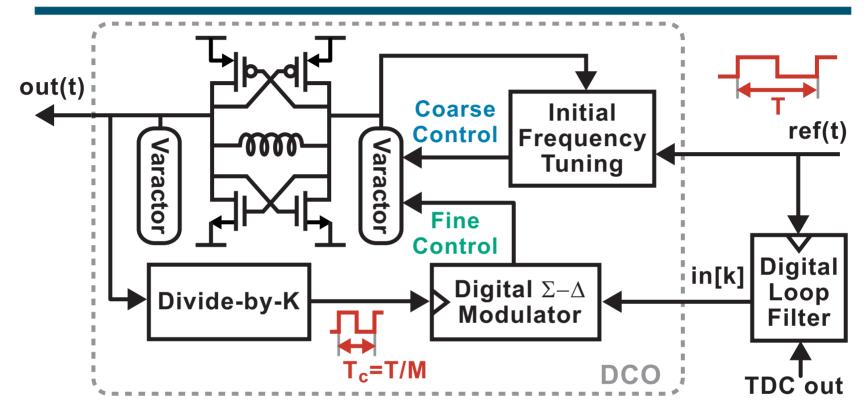

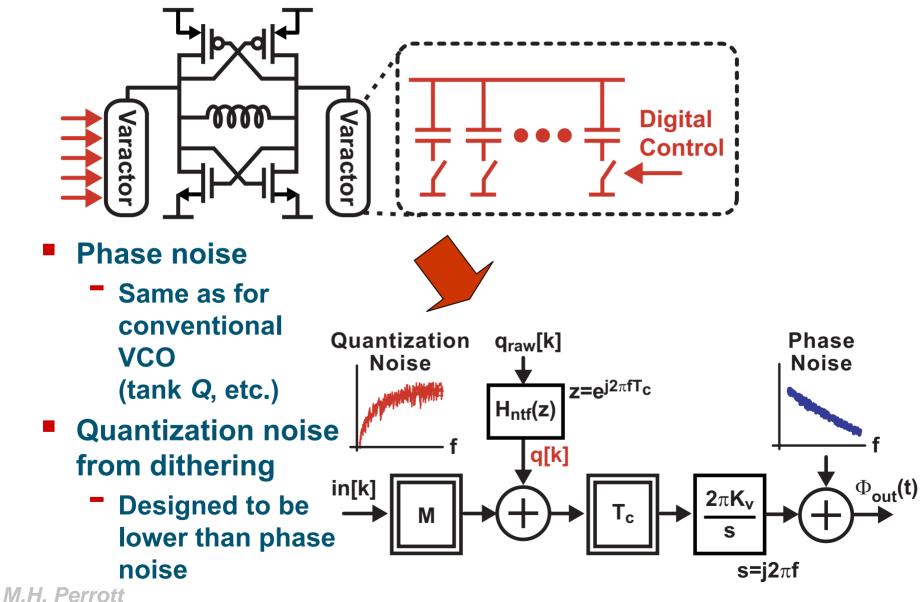

# Leveraging Dithering for Fine Control of DCO

- Increase resolution by  $\Sigma \Delta$  dithering of fine cap array

- Reduce noise from dithering by

- Using small unit caps in the fine cap array

- Increasing the dithering frequency (defined as  $1/T_c$ )

• Assume  $1/T_c = M/T$  (i.e. M times reference frequency)

### Noise Spectrum of a Switched Cap DCO

# Modeling

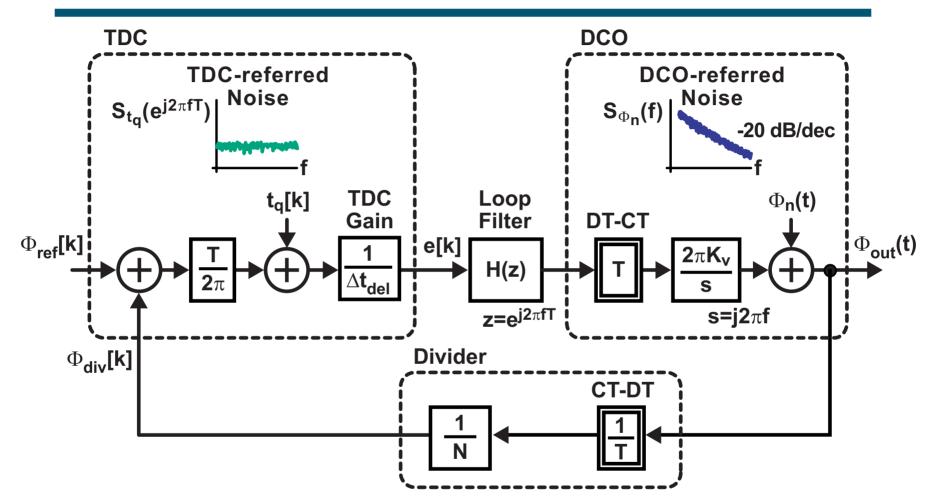

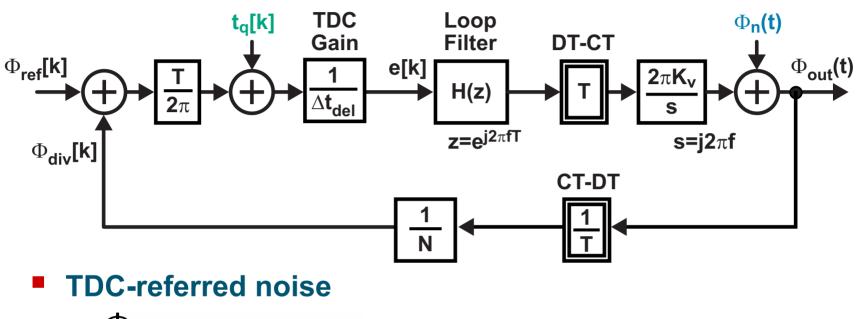

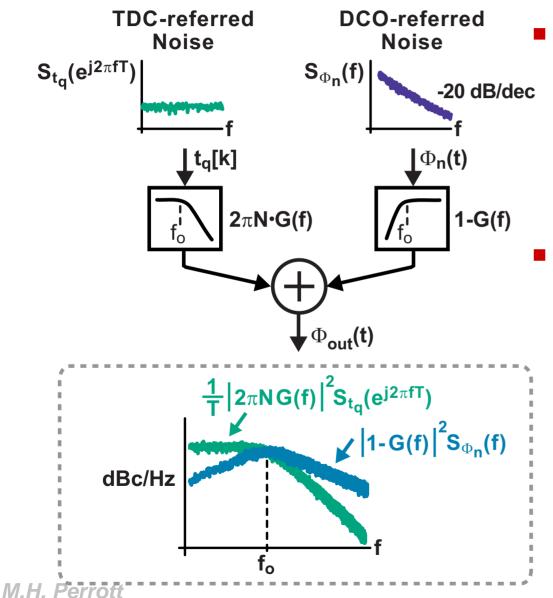

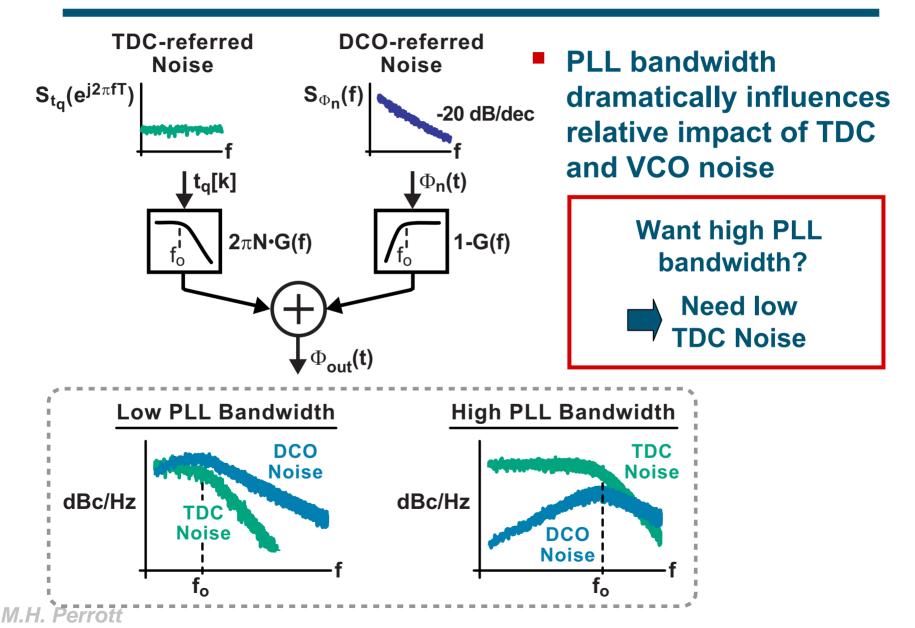

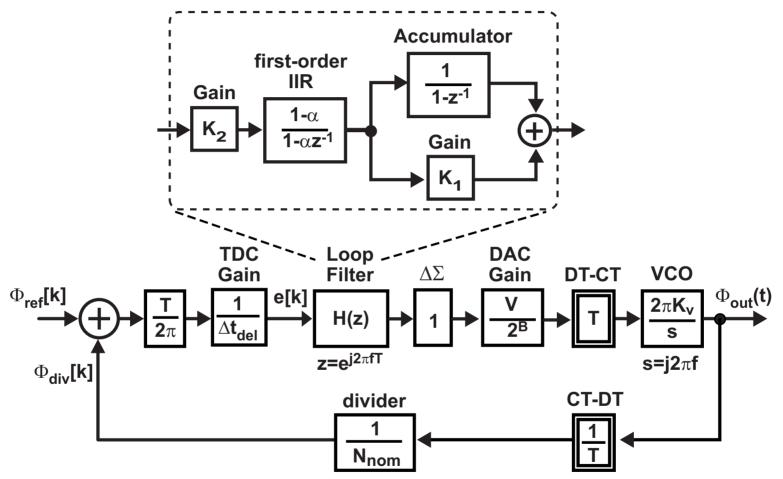

# **Overall Digital PLL Model**

TDC and DCO-referred noise influence overall phase noise according to associated transfer functions to output

Calculations involve both discrete and continuous time M.H. Perrott

# **Key Transfer Functions**

TDC-referred noise

$$\frac{\Phi_{out}}{t_q} = \frac{(1/\Delta t_{del})H(e^{j2\pi fT})T2\pi K_v/(2\pi jf)}{1+(1/\Delta t_{del})H(e^{j2\pi fT})TK_v/(2\pi jf)(1/N)}$$

#### DCO-referred noise

$$\frac{\Phi_{out}}{\Phi_n} = \frac{1}{1 + (1/\Delta t_{del})H(e^{j2\pi fT})TK_v/(2\pi jf)(1/N)}$$

# Utilize G(f) as a Parameterizing Function

Define open loop transfer function A(f) as:

$$A(f) = (1/\Delta t_{del})H(e^{j2\pi fT})TK_v/(2\pi jf)(1/N)$$

Define closed loop parameterizing function G(f) as:

$$G(f) = \frac{A(f)}{1 + A(f)}$$

Note: G(f) is a lowpass filter with DC gain = 1

M.H. Perrott

## **Transfer Function Parameterization Calculations**

#### TDC-referred noise

$$\frac{\Phi_{out}}{t_q} = \frac{(1/\Delta t_{del})H(e^{j2\pi fT})T2\pi K_v/(2\pi jf)}{1+(1/\Delta t_{del})H(e^{j2\pi fT})TK_v/(2\pi jf)(1/N)}$$

$$= \frac{2\pi NA(f)}{1+A(f)} = 2\pi NG(f)$$

DCO-referred noise

$$\frac{\Phi_{out}}{\Phi_n} = \frac{1}{1 + (1/\Delta t_{del})H(e^{j2\pi fT})TK_v/(2\pi jf)(1/N)}$$

$$= \frac{1}{1 + A(f)} = \frac{1 + A(f) - A(f)}{1 + A(f)} = \frac{1 - G(f)}{1 - G(f)}$$

# **Key Observations**

$$\frac{\Phi_{out}}{t_q} = 2\pi NG(f)$$

Lowpass with a DC gain of 2πN

### DCO-referred noise

$$\frac{\Phi_{out}}{\Phi_n} = 1 - G(f)$$

Highpass with a high frequency gain of 1

How do we calculate the output phase noise?

# **Spectral Density Calculations**

$$CT \rightarrow CT \xrightarrow{x(t)} H(f) \xrightarrow{y(t)} H(f)$$

$$DT \rightarrow DT \xrightarrow{x[k]} H(e^{j2\pi fT}) \xrightarrow{y[k]} H(f) \xrightarrow{y(t)} H(f) \xrightarrow{$$

• CT  $\rightarrow$  CT  $\qquad S_y(f) = |H(f)|^2 S_x(f)$

• DT  $\rightarrow$  DT  $S_y(e^{j2\pi fT}) = |H(e^{j2\pi fT})|^2 S_x(e^{j2\pi fT})$ • DT  $\rightarrow$  CT  $S_y(f) = \frac{1}{T} |H(f)|^2 S_x(e^{j2\pi fT})$

### **Phase Noise Calculation**

**TDC noise**

- DT to CT calculation

- Dominates PLL phase noise at low frequency offsets

# DCO noise

- CT to CT calculation

- Dominates PLL phase noise at high frequency offsets

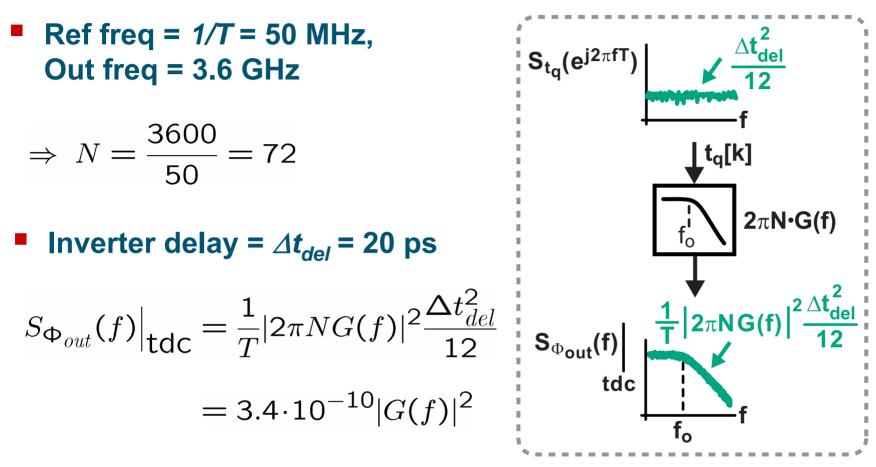

### **Example Calculation for Delay Chain TDC**

Note: G(f) = 1 at low offset frequencies

$10 \log(3.4 \cdot 10^{-10}) = -94.7 \ dBc/Hz$  (at low offset freq.)

## **CAD Tools**

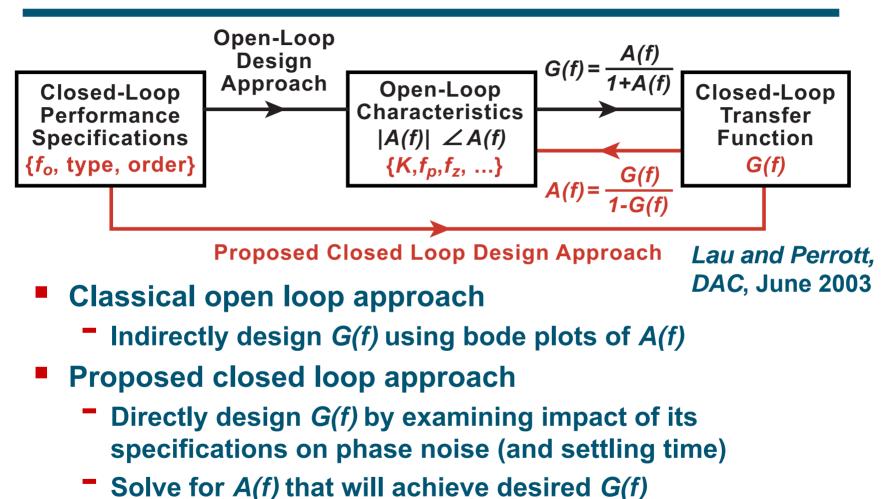

# **Closed Loop PLL Design Approach**

Implemented in PLL Design Assistant Software

http://www.cppsim.com

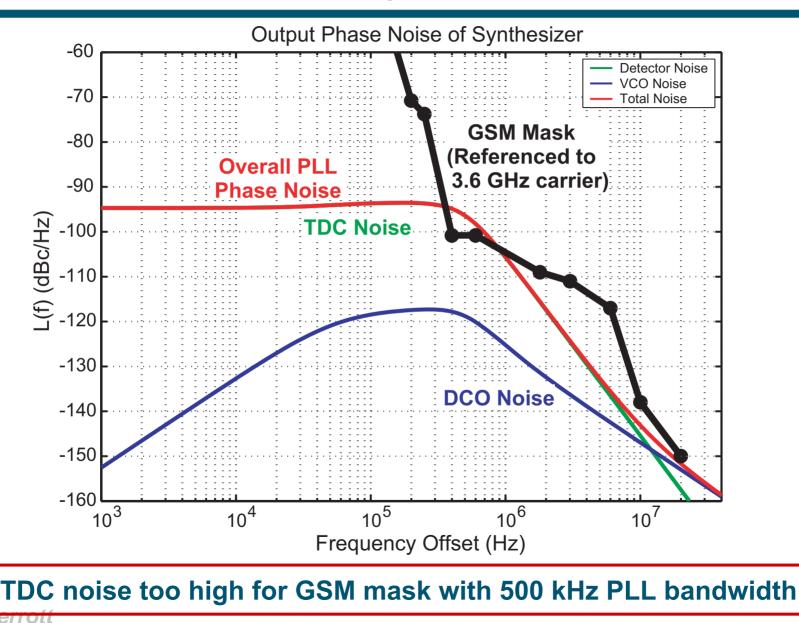

## Evaluate Phase Noise with 500 kHz PLL Bandwidth

#### Key PLL parameters:

- G(f): 500 kHz BW, Type II, 2<sup>nd</sup> order rolloff

- TDC noise: -94.7 dBc/Hz

- DCO noise: -153 dBc/Hz at 20 MHz offset (3.6 GHz carrier)

| PLL Design Assistant                                                              |                                    |    |          |          |                            |                  |      |                  |      |

|-----------------------------------------------------------------------------------|------------------------------------|----|----------|----------|----------------------------|------------------|------|------------------|------|

| File Edit Templates                                                               |                                    |    |          |          |                            |                  |      |                  |      |

| Dynamic Parameters                                                                | paris. pole Hz On Noise Parameters |    |          |          |                            | eters            |      |                  |      |

| fo 500e3 Hz                                                                       | paris. Q                           |    | _        | On       | ref. freq                  | 50e6             |      | Hz               |      |

| order C1 C2 C3                                                                    | paris. pole                        |    | Hz       |          | out freq.                  | 3.6e9            |      | Hz 🚺             |      |

| shape <ul> <li>Butter C Bessel</li> <li>C Cheby1 C Cheby2 C Elliptical</li> </ul> | paris. Q                           |    |          | On       | Detector                   | -94.7            |      | dBc/Hz           | On   |

| ripple dB                                                                         | paris.pole                         |    | Hz<br>Hz | On       | VCO                        | -153             |      | dBc/Hz           | On   |

| type C1 © 2                                                                       | paris. zero                        |    | -<br>Hz  | On       |                            | set 20e6         |      | Hz               |      |

| fz/ro, 1/10                                                                       | paris. zero                        |    | Hz       | On       | S-D C 1<br>C 3 C           | 0 2 0n           |      | ***              | On   |

| Resulting Open Loop Par                                                           | ameters                            |    |          |          | Resulting Plots and Jitter |                  |      |                  |      |

| K: 7.509e+011 alt                                                                 | er:                                | On |          |          |                            | Zero Diagram     |      | ansfer Func      | tion |

| fp: 7.655e+005 Hz alt                                                             | er:                                | On | Apply    | <u>y</u> | 1e3                        | Response<br>40e6 | -160 | oise Plot<br>-60 |      |

| fz: 5.000e+004 Hz alt                                                             | er:                                | On |          |          |                            |                  | -100 | -80              |      |

| Qp:alt                                                                            | er:                                | On |          | rms j    | itter: 980.78              | 8 fs             |      |                  |      |

| PLL Design As                                                                     |                                    |    |          |          |                            |                  |      |                  |      |

| . Perrott                                                                         |                                    |    |          |          |                            |                  |      |                  |      |

### Calculated Phase Noise Spectrum with 500 kHz BW

32

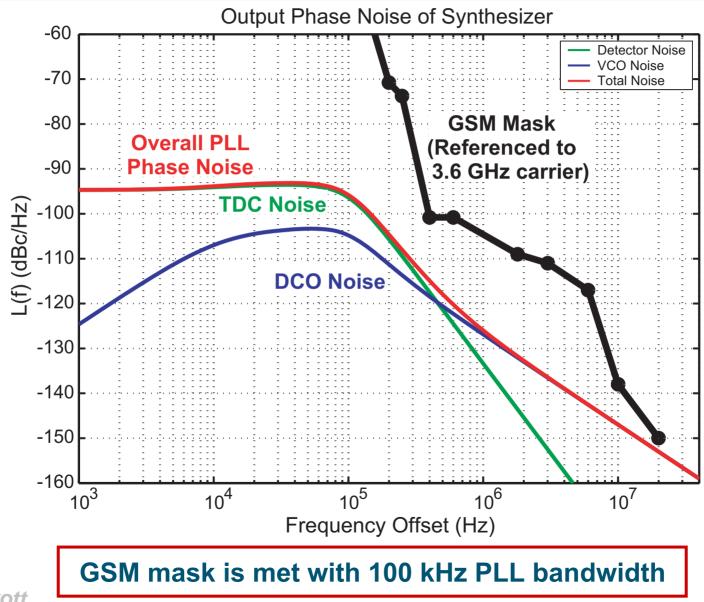

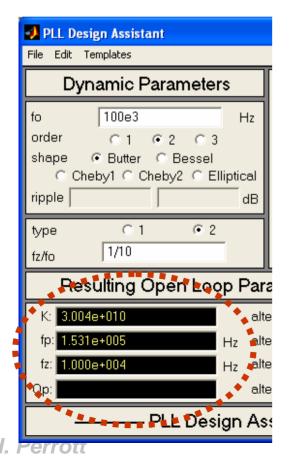

### Change PLL Bandwidth to 100 kHz

#### Key PLL parameters:

- G(f): 100 kHz BW, Type = 2, 2<sup>nd</sup> order rolloff

- TDC noise: -94.7 dBc/Hz

- DCO noise: -153 dBc/Hz at 20 MHz offset (3.6 GHz carrier)

| PLL Design Assistant<br>File Edit Templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |                            |                                        |                  |                         |                                    |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|------------------|-------------------------|------------------------------------|----------------|

| Dynamic Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | paris. pole Hz On                                                                               |                            |                                        | Noise Parameters |                         |                                    |                |

| fo 100e3 Hz<br>order 2 3<br>shape © Butter © Bessel<br>© Cheby1 © Cheby2 © Elliptical<br>ripple dB<br>type © 1 © 2<br>fz/fo 1/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | paris. Q<br>paris. pole<br>paris. Q<br>paris. pole<br>paris. pole<br>paris. zero<br>paris. zero | Hz<br>Hz<br>Hz<br>Hz<br>Hz | On<br>On<br>On<br>On<br>On<br>On<br>On | out freq.        | C 2 On                  | Hz<br>Hz<br>dBc/Hz<br>dBc/Hz<br>Hz | On<br>On<br>On |

| Resulting Open Loop Par                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ameters                                                                                         |                            | Resulting Plots and Jitter             |                  |                         |                                    |                |

| K:     3.004e+010     altrain the second sec | er: 0n<br>er: 0n                                                                                | Appl                       |                                        |                  | esponse (*<br>40e6 -160 | Transfer Fund<br>Noise Plot        | ction          |

| Op:       On       rms jitter:       464.961 fs         PLL Design Assistant       Written by Michael Perrott (http://www-mtl.mit.edu/~perrott)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |                            |                                        |                  |                         |                                    |                |

## Calculated Phase Noise Spectrum with 100 kHz BW

# Loop Filter Design using PLL Design Assistant

PLL Design Assistant allows fast loop filter design

See Section 4 of Supplemental Slides

Assumption: Type = 2, 2<sup>nd</sup> order rolloff

$$H(z) = K_{LF} \left(\frac{1}{1-z^{-1}}\right) \frac{1-b_1 z^{-1}}{1-a_1 z^{-1}}$$

- Where:

$a_1 = \frac{1}{1+w_p T}$   $b_1 = \frac{1}{1+w_z T}$

$K_{LF} = \left(\frac{\Delta t_{del}}{T/N}\right) \frac{K}{K_v} \left(\frac{w_p}{w_z}\right) \frac{a_1}{b_1} T$

PLL Design Assistant provides the values of *K*,  $w_p = 2\pi f_p$ ,  $w_z = 2\pi f_z$

35

### **Example Digital Loop Filter Calculation**

#### Assumptions

- Ref freq (1/T) = 50 MHz, Out freq = 3.6 GHz (so N = 72)

- $\Delta t_{del}$  = 20 ps,  $K_v$  = 12 kHz/unit cap

- 100 kHz bandwidth, Type = 2, 2<sup>nd</sup> order rolloff

|        | <b>4</b> PLL Design Assistant                                                                 |          |      |

|--------|-----------------------------------------------------------------------------------------------|----------|------|

|        | File Edit Templates                                                                           |          |      |

|        | Dynamic Parameters                                                                            | \$       |      |

|        | fo 100e3<br>order C1 © 2 C 3<br>shape © Butter © Bessel<br>© Cheby1 © Cheby2 © Elli<br>ripple | <u> </u> |      |

|        | type 0 1 0 2<br>fz/fo 1/10                                                                    |          |      |

|        | Resulting Open Loo                                                                            | pΡ       | ara  |

|        | K: 3.004e+010                                                                                 | *        | alte |

|        | fp: 1.531e+005                                                                                | Ηz       | alte |

|        | fz: 1.000e+004                                                                                | Ηz       | alte |

|        | Qp:                                                                                           | •**      | alte |

|        | PLE Desig                                                                                     | ر n      | As   |

| M.H. I | Perrott                                                                                       |          |      |

$$H(z) = K_{LF} \left(\frac{1}{1-z^{-1}}\right) \frac{1-b_1 z^{-1}}{1-a_1 z^{-1}}$$

$$b_1 = \frac{1}{1+2\pi 10 \text{kHz/50MHz}} = \boxed{.9987}$$

$$a_1 = \frac{1}{1+2\pi 153 \text{kHz/50MHz}} = \boxed{.9811}$$

$$K_{LF} = \left(\frac{\Delta t_{del}}{T/N}\right) \frac{3 \cdot 10^{10}}{12 \text{kHz}} \frac{153}{10} \frac{.9811}{.9987} \frac{1}{50 \text{MHz}}$$

$$= \left(\frac{\Delta t_{del}}{T/N}\right) 0.75 = \left(\frac{\Delta t_{del}}{T_{dco}}\right) 0.75$$

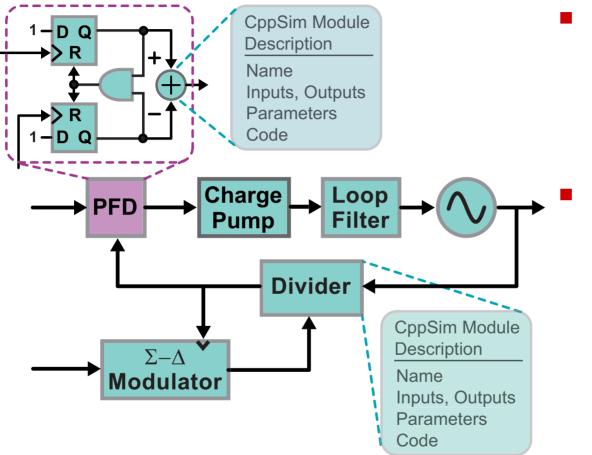

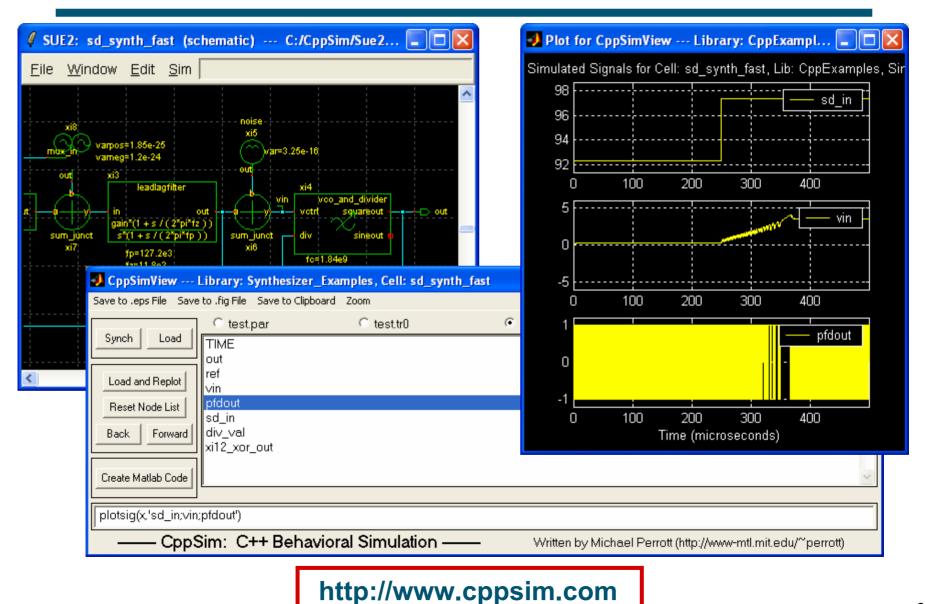

# Verify Calculations Using C++ Behavioral Modeling

Schematic

- Hierarchical description of system topology

- **Code blocks**

- Specification of *module behavior* using templated C++ code

Behavioral environment allows efficient architectural investigation and validation of calculations

Fast simulation speed is essential for design investigation M.H. Perrott

# CppSim – A Fast C++ Behavioral Simulator

### How Do We Improve TDC Performance?

- Two Key Issues: TDC resolution Mismatch

# **Motivation**

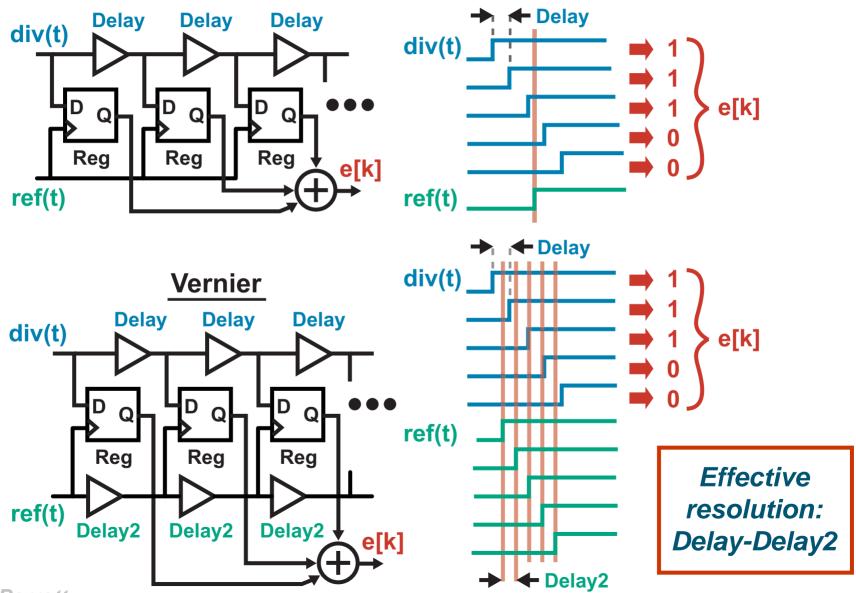

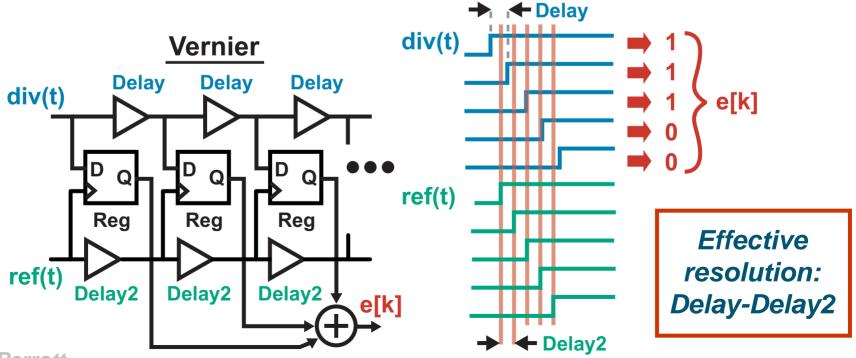

### Improve Resolution with Vernier Delay Technique

#### **Issues with Vernier Approach**

- Mismatch issues are more severe than the single delay chain TDC

- Reduced delay is formed as *difference* of two delays

- Large measurement range requires large area

- Initial PLL frequency acquisition may require a large range

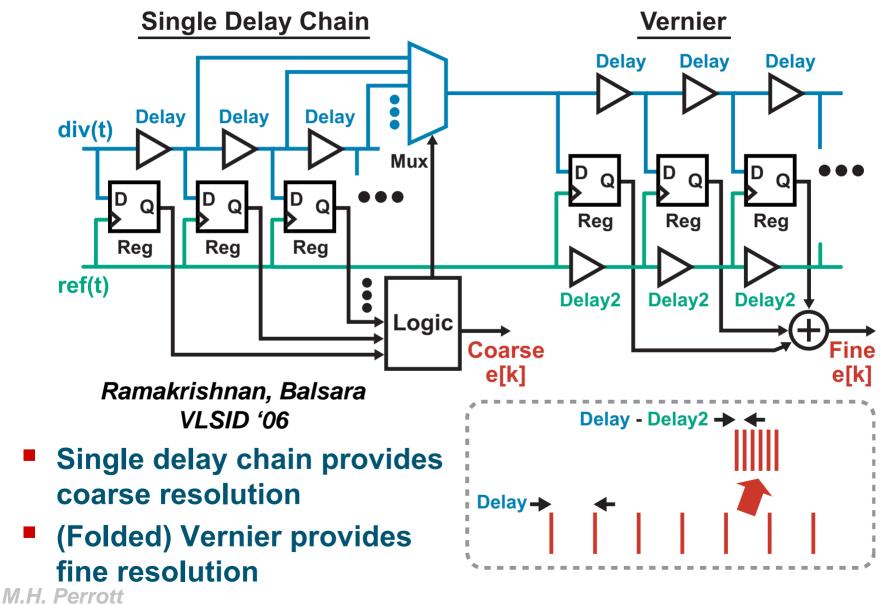

### **Two-Step TDC Architecture Allows Area Reduction**

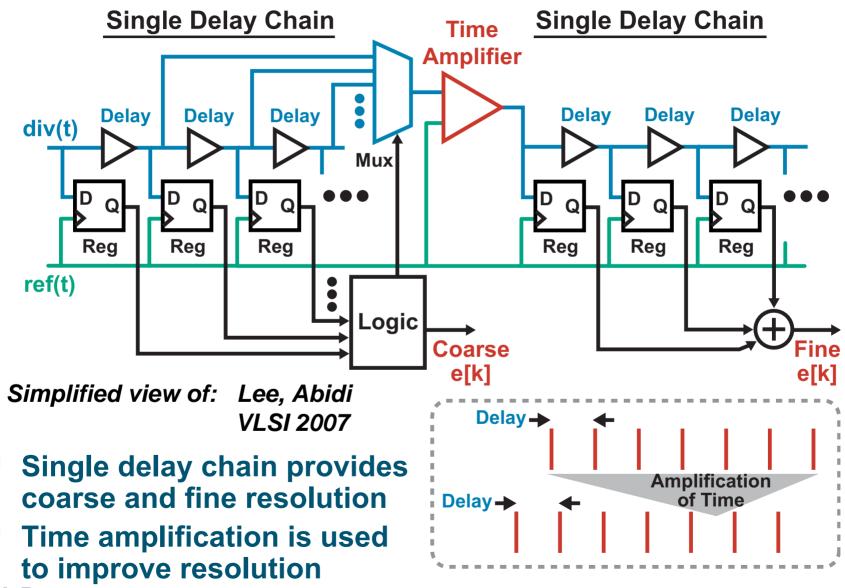

# **Two-Step TDC Using Time Amplification**

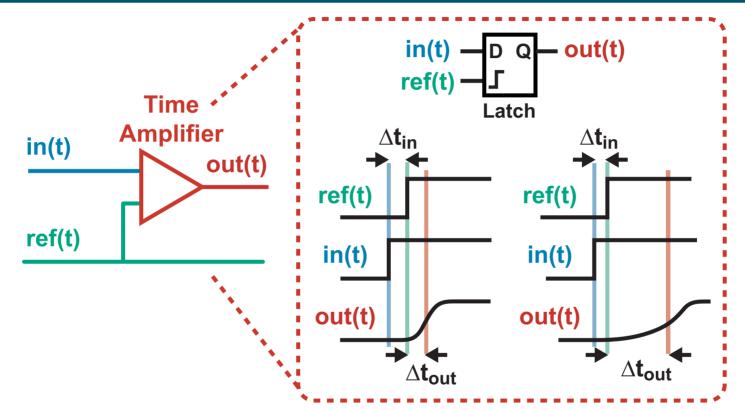

### Leveraging Metastability to Create a Time Amplifier

Simplified view of: Abas, et al., Electronic Letters, Nov 2002 (note that actual implementation uses SR latch)

Metastability leads to progressively slower output transitions as setup time on latch is encroached upon

Time difference at input is amplified at output M.H. Perrott

### Interpolating time-to-digital converter

- Interpolate between edges to achieve fine resolution

- Cyclic approach can also be used for large range

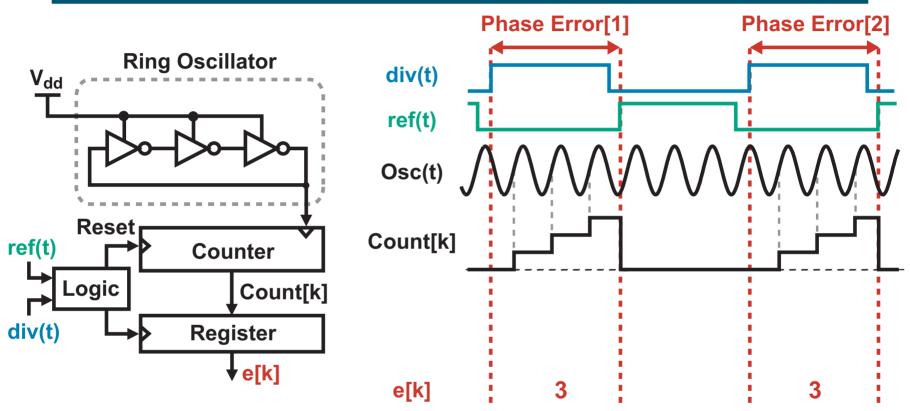

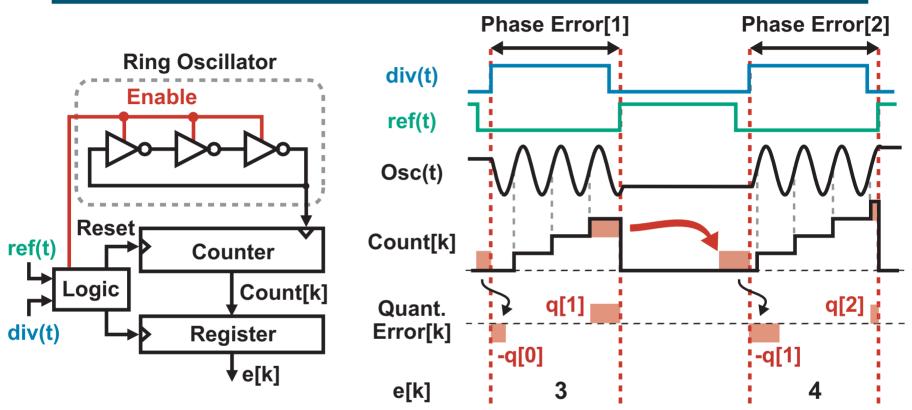

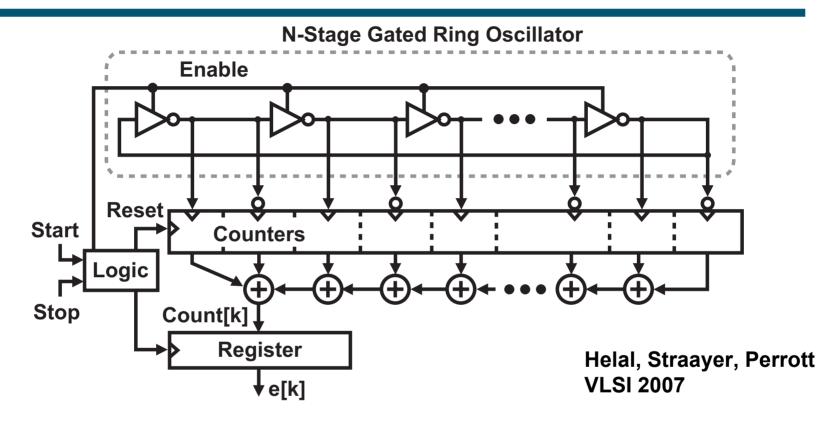

### An Oscillator-Based TDC

Output e[k] corresponds to the number of oscillator edges that occur during the measurement time window

#### Advantages

Extremely large range can be achieved with compact area

Quantization noise is scrambled across measurements M.H. Perrott

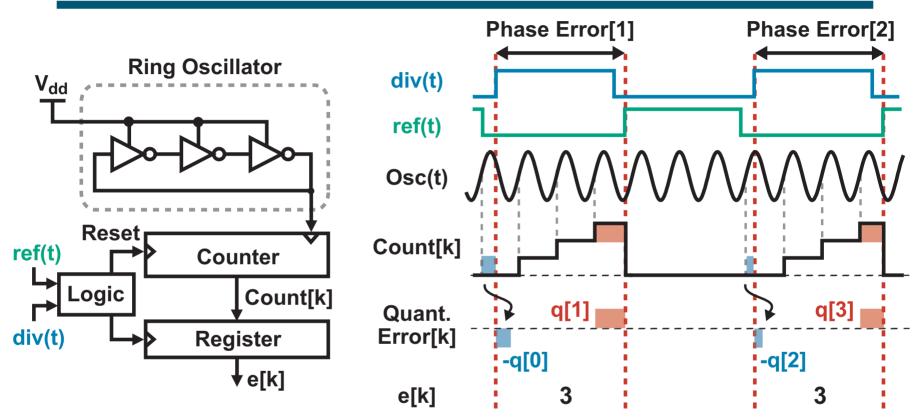

# A Closer Look at Quantization Noise Scrambling

- Quantization error occurs at beginning and end of each measurement interval

- As a rough approximation, assume error is uncorrelated between measurements

Averaging of measurements improves effective resolution *M.H. Perrott*

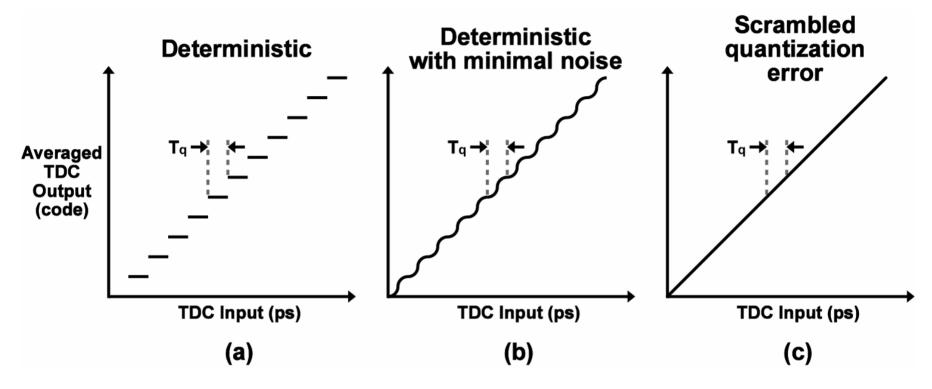

#### Deterministic quantizer error vs. scrambled error

- Deterministic TDC do not provide inherent scrambling

- For oversampling benefit, *TDC error must be scrambled!*

- Some systems provide input scrambling ( $\Delta\Sigma$  fractional-N PLL), while some others do not (integer-N PLL)

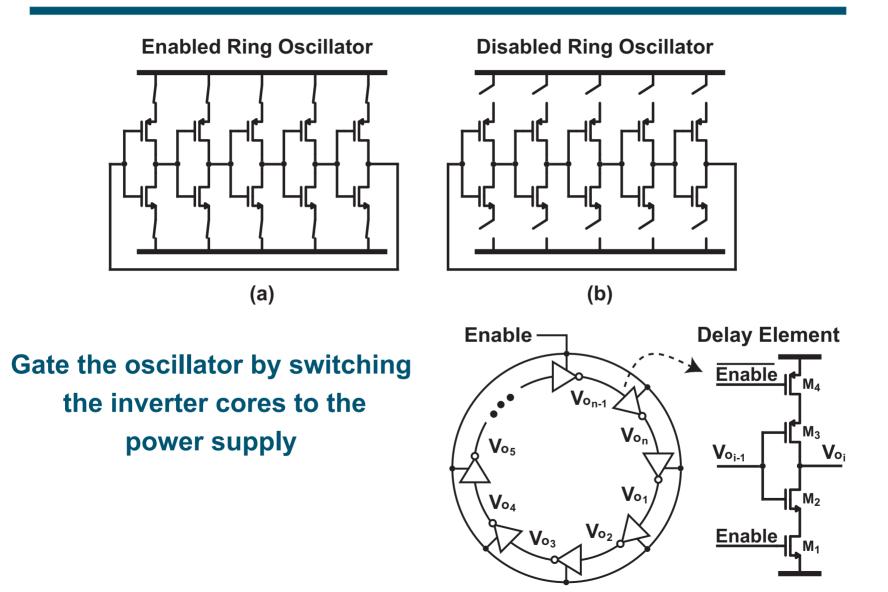

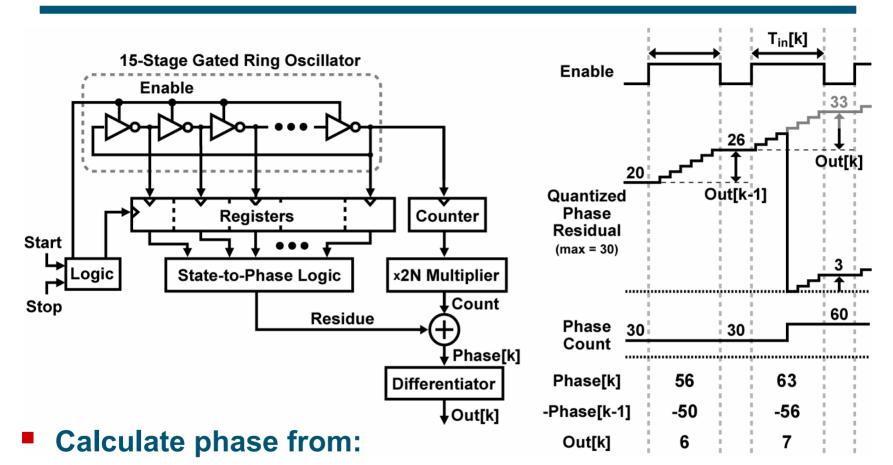

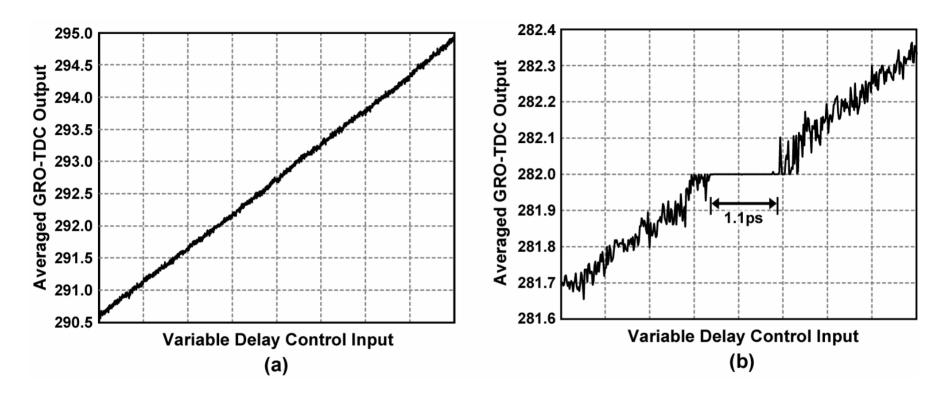

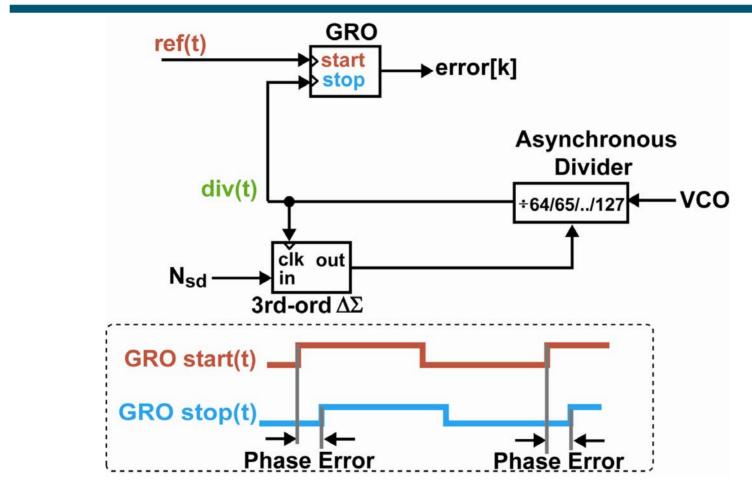

### **Proposed GRO TDC Structure**

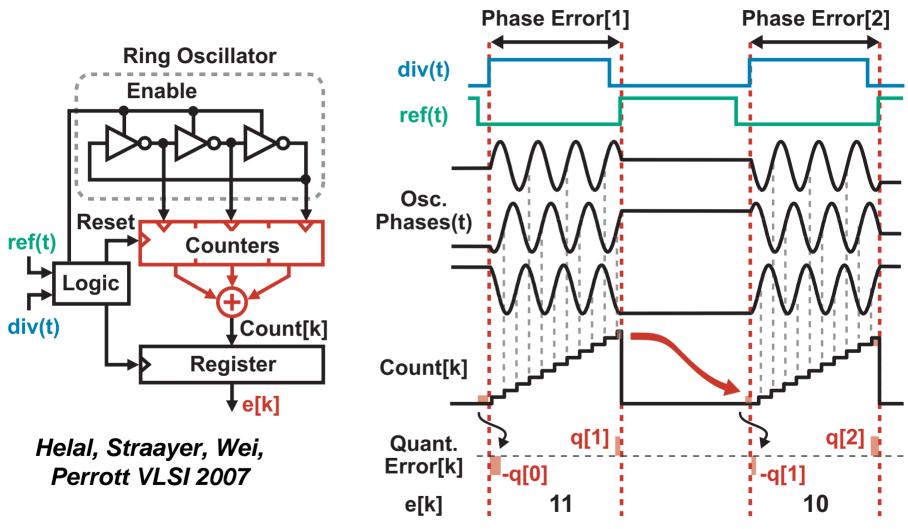

# A Gated Ring Oscillator (GRO) TDC

Enable ring oscillator only during measurement intervals

- Hold the state of the oscillator between measurements

- Quantization error becomes first order noise shaped!

- e[k] = Phase Error[k] + q[k] q[k-1]

Averaging dramatically improves resolution!

### Improve Resolution By Using All Oscillator Phases

Raw resolution is set by inverter delay

M.H. Performent resolution is dramatically improved by averaging 52

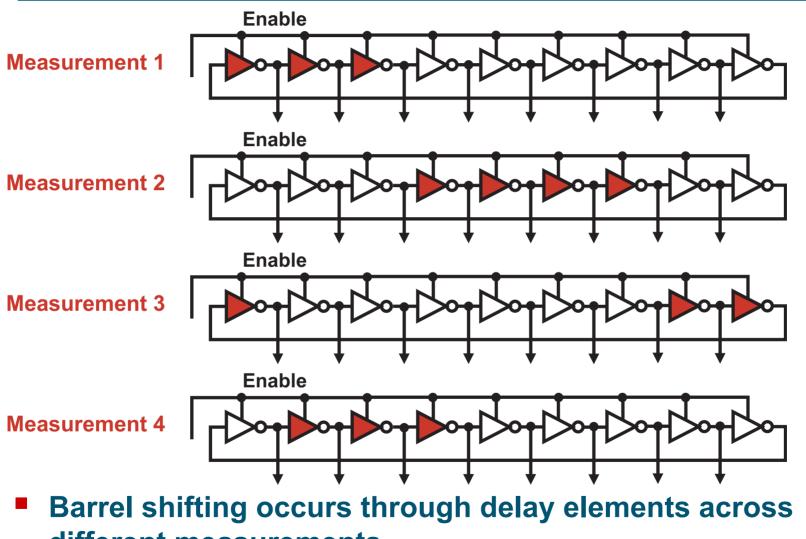

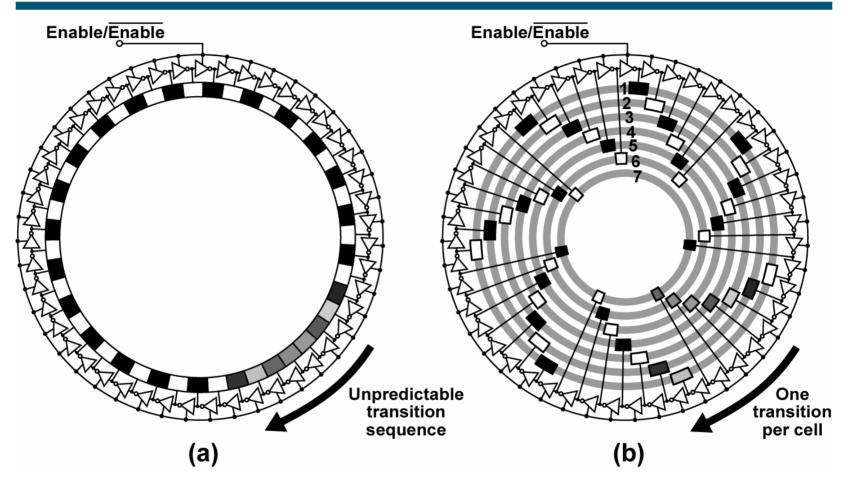

### **GRO TDC Also Shapes Delay Mismatch**

different measurements

Mismatch between delay elements is first order shaped!

### Simple gated ring oscillator inverter-based core

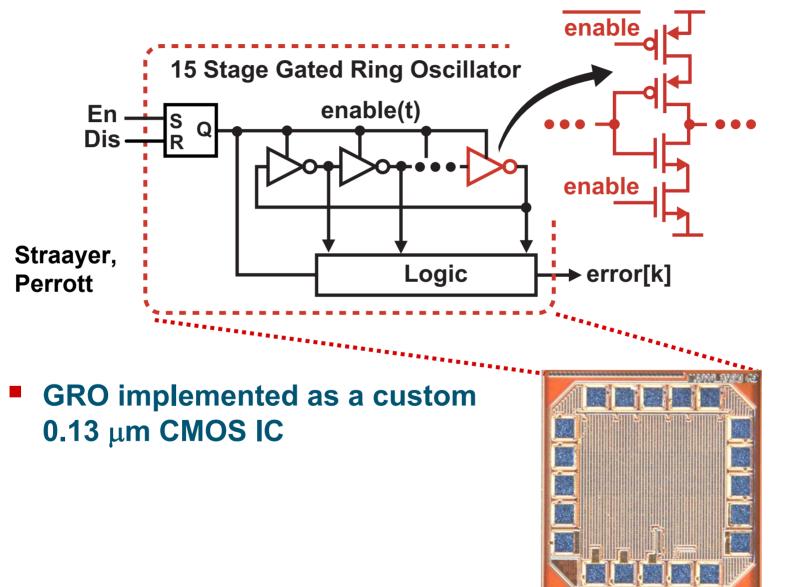

### **GRO** Prototype

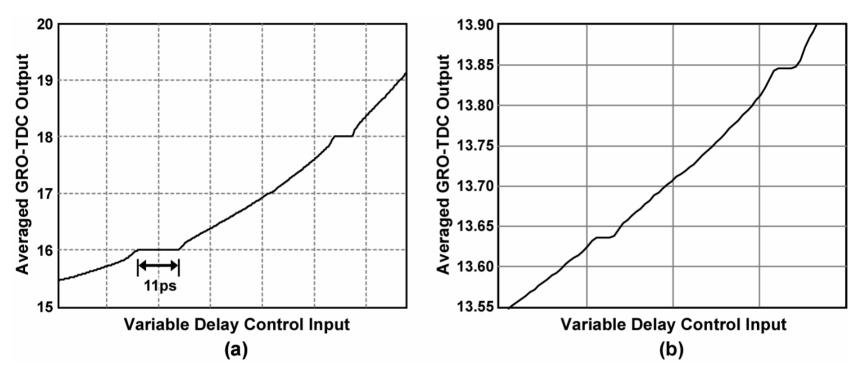

### Measured GRO Results Confirm Noise Shaping

### Measured deadzone behavior of inverter-based GRO

- Deadzones were caused by errors in gating the oscillator

- GRO "injection locked" to an integer ratio of F<sub>S</sub>

- Behavior occurred for almost all integer boundaries, and some fractional values as well

- Noise shaping benefit was limited by this gating error

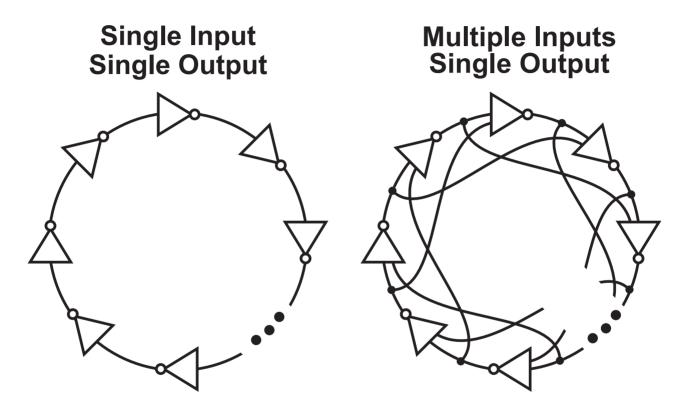

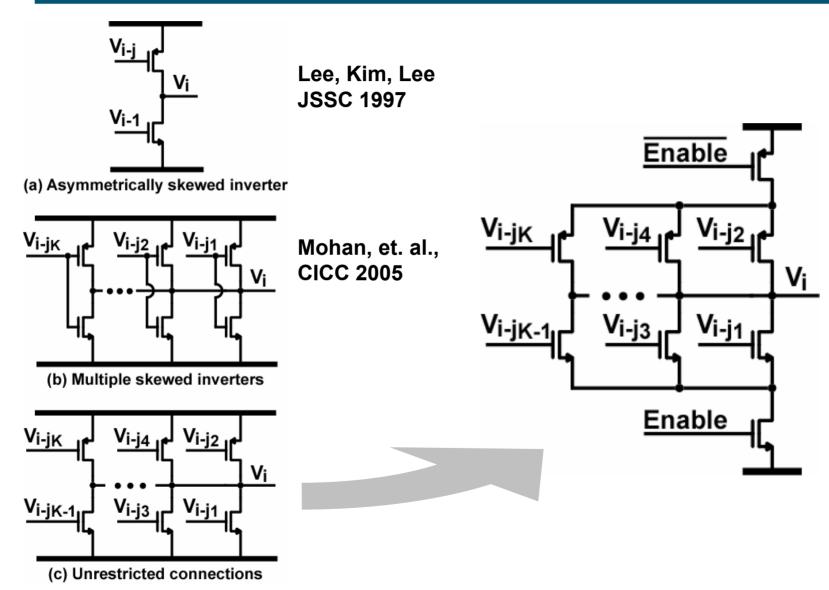

### Next Generation GRO: Multi-path oscillator concept

- Use multiple inputs for each delay element instead of one

- Allow each stage to optimally begin its transition based on information from the entire GRO phase state

- Key design issue is to ensure primary mode of oscillation

#### Multi-path inverter core

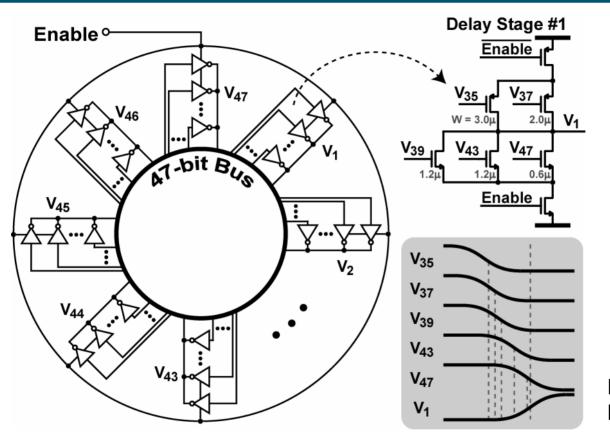

### Proposed multi-path gated ring oscillator

Hsu, Straayer, Perrott ISSCC 2008

- Oscillation frequency near 2GHz with 47 stages...

- Reduces effective delay per stage by a factor of 5-6!

- Represents a factor of 2-3 improvement compared to previous multi-path oscillators

### A simple measurement approach...

- 2 counters per stage \* 47 stages = 94 counters each at 2GHz

- Power consumption for these counters is unreasonable

Need a more efficient way to measure the multi-path GRO

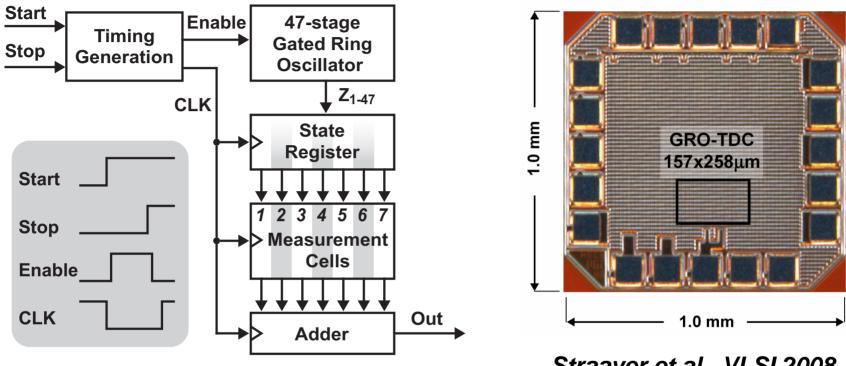

# **Count Edges by Sampling Phase**

- A single counter for coarse phase information (keeps track of phase wrapping)

- GRO phase state for fine count information

■ 1 counter and N registers → much more efficient M.H. Perrott

#### **Proposed Multi-Path Measurement Structure**

Multi-path structure leads to ambiguity in edge position

Partition into 7 cells to avoid such ambiguity

Requires 7 counters rather than 1, but power still OK M.H. Perrott

### **Prototype 0.13µm CMOS multi-path GRO-TDC**

Straayer et al., VLSI 2008

- Two implemented versions:

- 8-bit, 500Msps

- 11-bit, 100Msps version

2-21mW power consumption depending on input duty cycle

M.H. Perrott

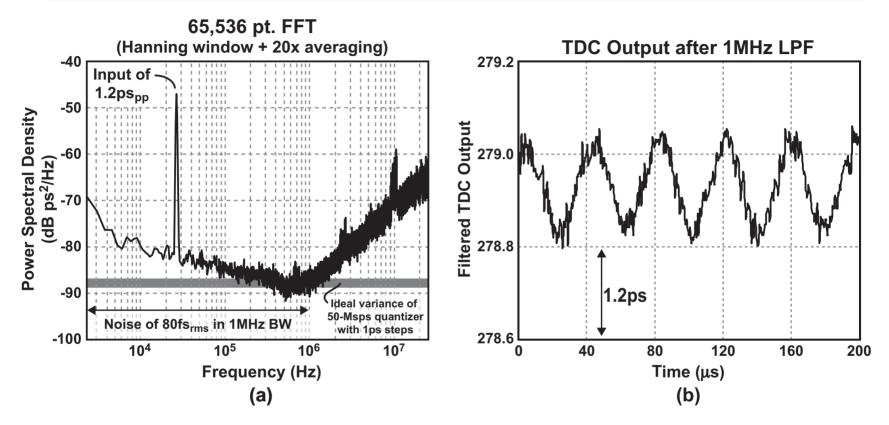

### Measured noise-shaping of multi-path GRO

- Data collected at 50Msps

- More than 20dB of noise-shaping benefit

- 80fs<sub>rms</sub> integrated error from 2kHz-1MHz

Floor primarily limited by 1/f noise (up to 0.5-1MHz) M.H. Perrott

### Measured deadzone behavior for multi-path GRO

- Only deadzones for outputs that are multiples of 2N

- **94, 188, 282, etc.**

- No deadzones for other even or odd integers, fractional output

- Size of deadzone is reduced by 10x

The Issue of Quantization Noise Due to Divider Dithering

#### The Nature of the Quantization Noise Problem

• Increasing PLL bandwidth increases impact of  $\Delta\Sigma$  fractional-N noise

M.H. Perrott Cancellation offers a way out!

68

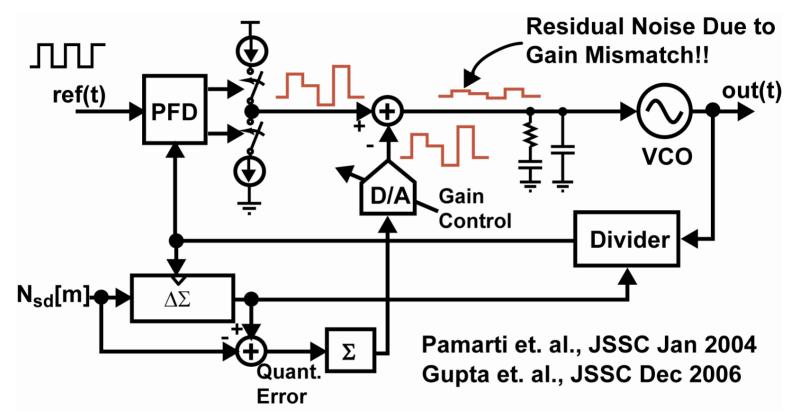

### **Previous Analog Quantization Noise Cancellation**

- Phase error due to ΔΣ is predicted by accumulating ΔΣ quantization error

- Gain matching between PFD and D/A must be precise

Matching in analog domain limits performance

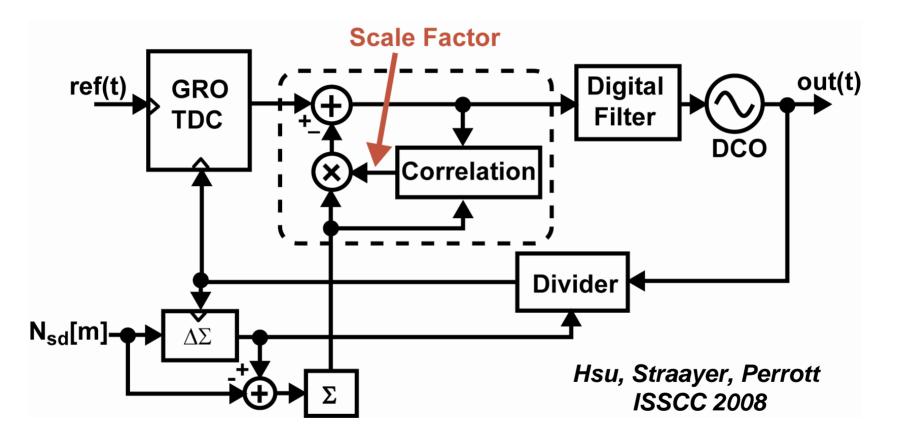

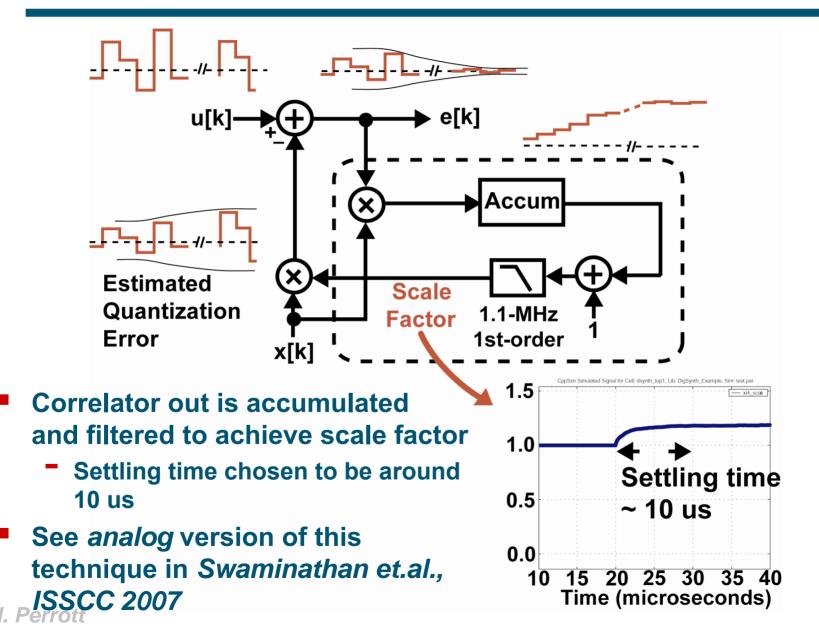

# **Proposed All-digital Quantization Noise Cancellation**

Scale factor determined by simple digital correlation

Analog non-idealities such as DC offset are completely eliminated

### **Details of Proposed Quantization Noise Cancellation**

71

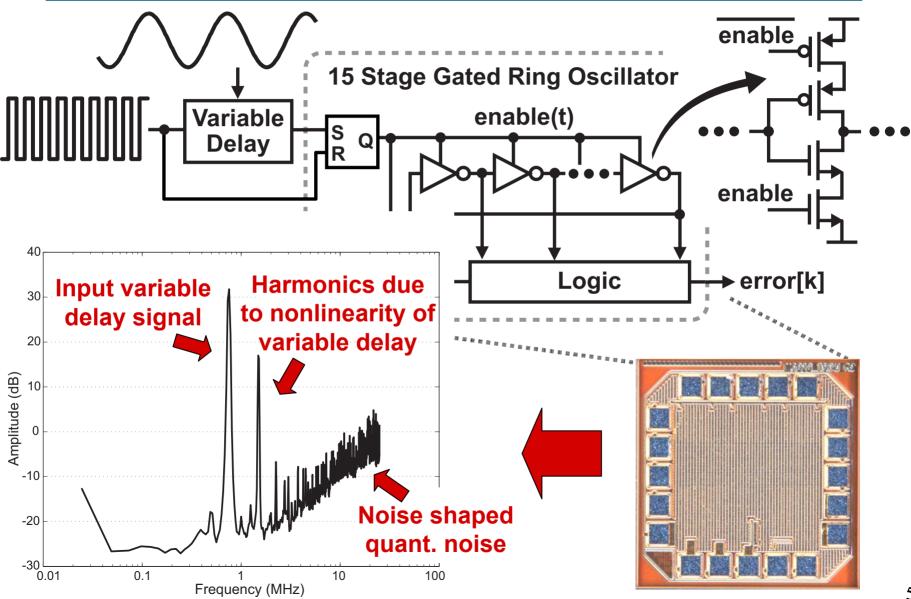

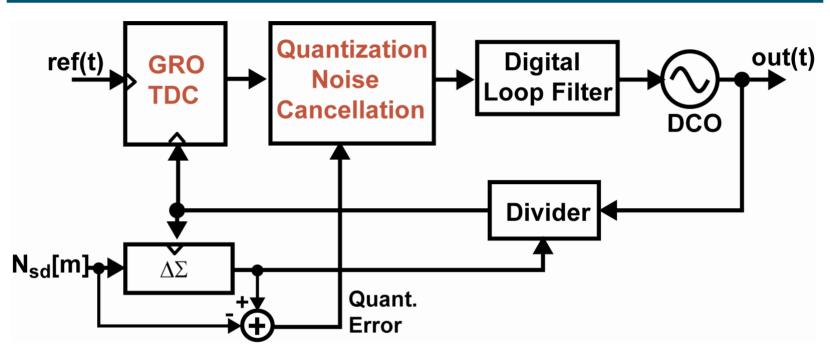

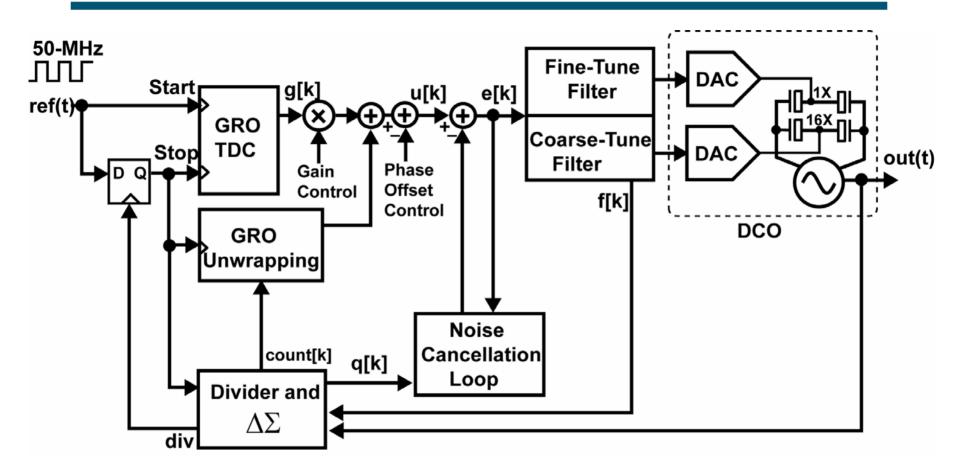

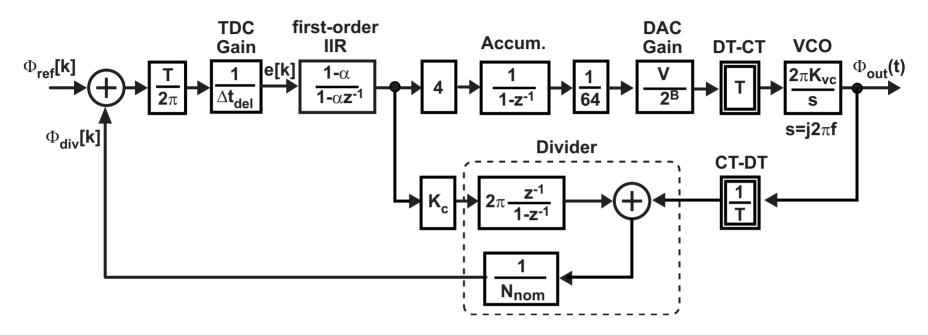

### **Proposed Digital Wide BW Synthesizer**

- Gated-ring-oscillator (GRO) TDC achieves low in-band noise

- All-digital quantization noise cancellation achieves low out-of-band noise

- Design goals:

- 3.6-GHz carrier, 500-kHz bandwidth

- <-100dBc/Hz in-band, <-150 dBc/Hz at 20 MHz offset</p>

#### **Overall Synthesizer Architecture**

#### Note: Detailed behavioral simulation model available at http://www.cppsim.com

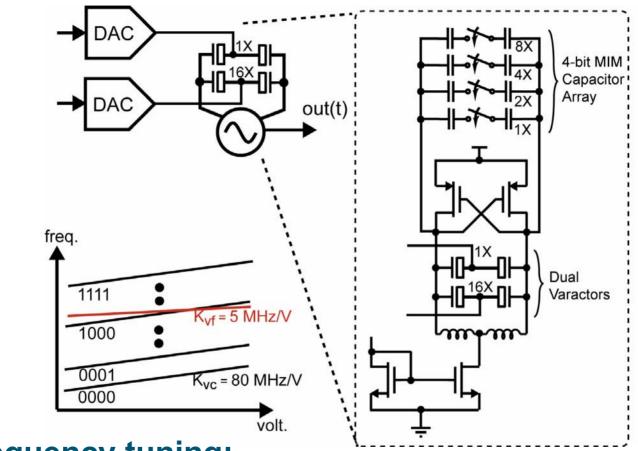

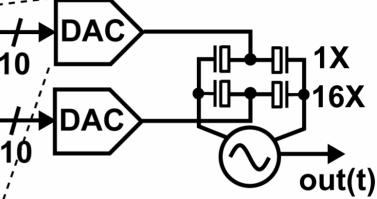

#### **Dual-Port LC VCO**

Frequency tuning:

- Use a small 1X varactor to minimize noise sensitivity

- Use another 16X varactor to provide moderate range

Use a four-bit capacitor array to achieve 3.3-4.1 GHz range M.H. Perrott

# **Digitally-Controlled Oscillator with Passive DAC**

- Goals of 10-bit DAC

- Monotonic

- 1X varactor minimizes noise sensitivity

- 16X varactor provides moderate range

- A four-bit capacitor array covers 3.3-4.1GHz

- Minimal active circuitry and no transistor bias currents

- Full-supply output range

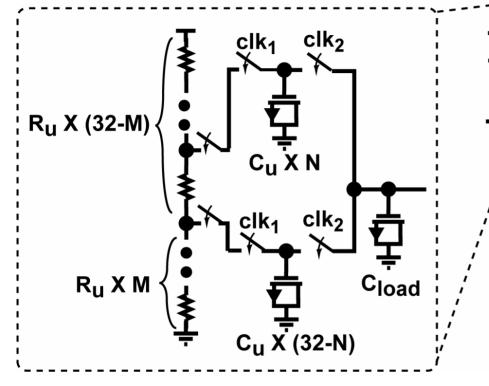

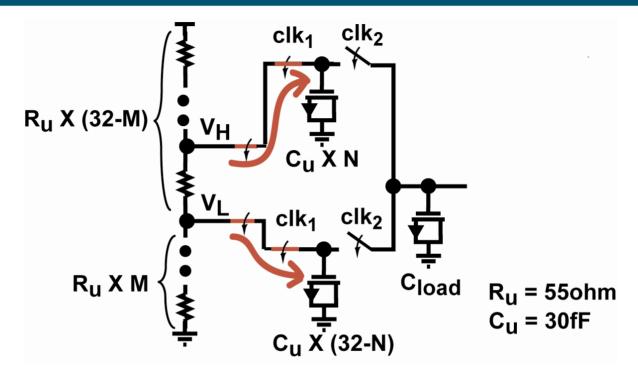

#### **Operation of 10-bit Passive DAC (Step 1)**

- 5-bit resistor ladder; 5-bit switch-capacitor array

- Step 1: Capacitors Charged

- Resistor ladder forms  $V_L = M/32 \cdot V_{DD}$  and  $V_H = (M+1)/32 \cdot V_{DD}$ , where M ranges from 0 to 31

- N unit capacitors charged to V<sub>H</sub>, and (32-N) unit capacitors charged to V<sub>L</sub>

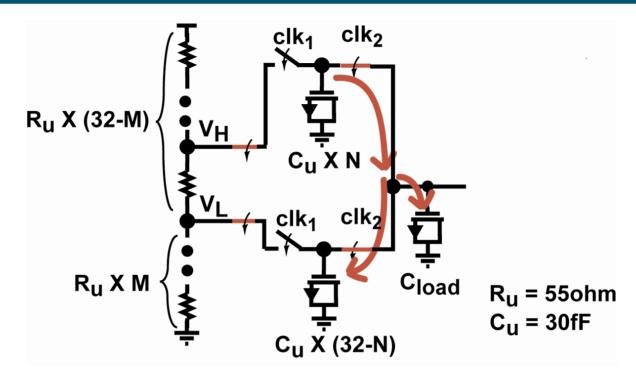

#### **Operation of 10-bit Passive DAC (Step 2)**

- Step 2: Disconnect Capacitors from Resistors, Then Connect Together

- Achieves DAC output with first-order filtering

- Bandwidth =  $32 \cdot C_u / (2\pi \cdot C_{load}) \cdot 50 \text{MHz}$

- Determined by capacitor ratio

- Easily changed by using different C<sub>load</sub>

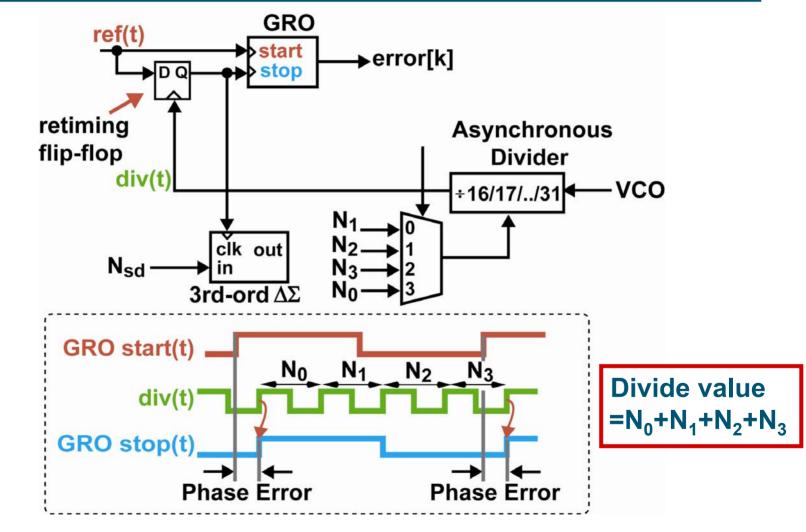

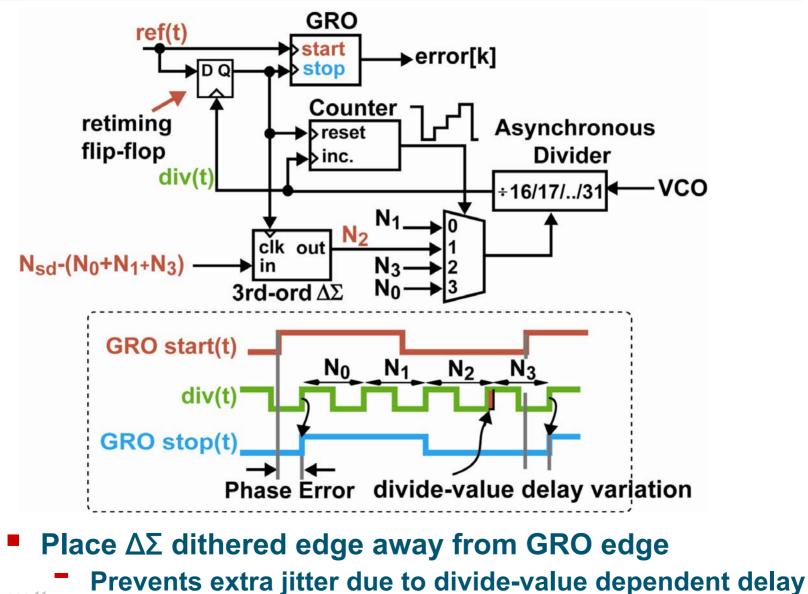

#### Now Let's Examine Divider ...

#### Issues:

GRO range must span entire reference period during initial lock-in

#### **Proposed Divider Structure**

#### Resample reference with 4x division frequency

Lowers GRO range to one fourth of the reference period

#### **Proposed Divider Structure (cont'd)**

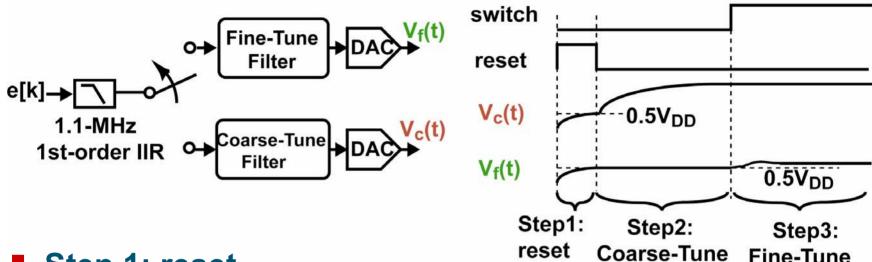

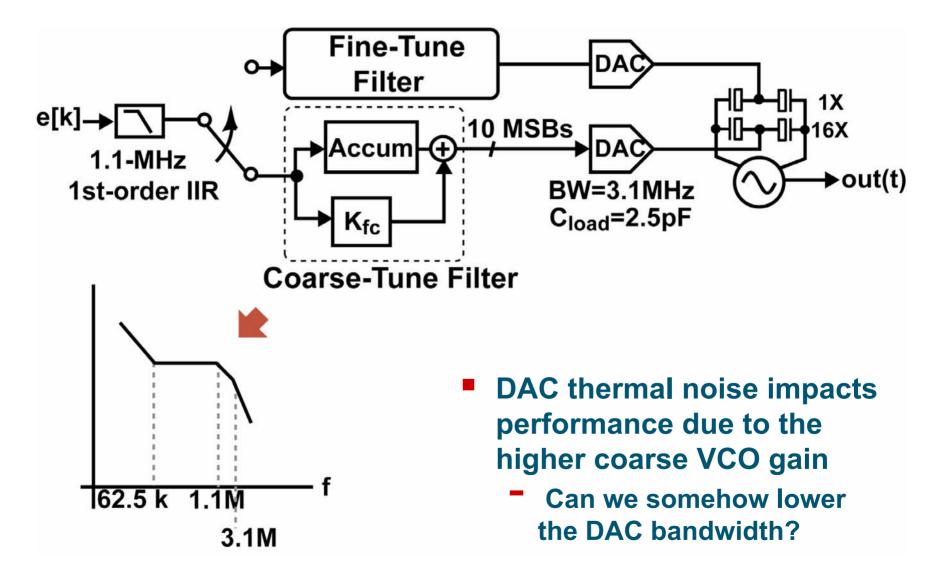

## **Dual-Path Loop Filter**

- Step 1: reset

- Step 2: frequency acquisition

- V<sub>c</sub>(t) varies

- V<sub>f</sub>(t) is held at midpoint

- Step 3: steady-state lock conditions

- V<sub>c</sub>(t) is frozen to take quantization noise away

ΔΣ quantization noise cancellation is enabled M.H. Perrott

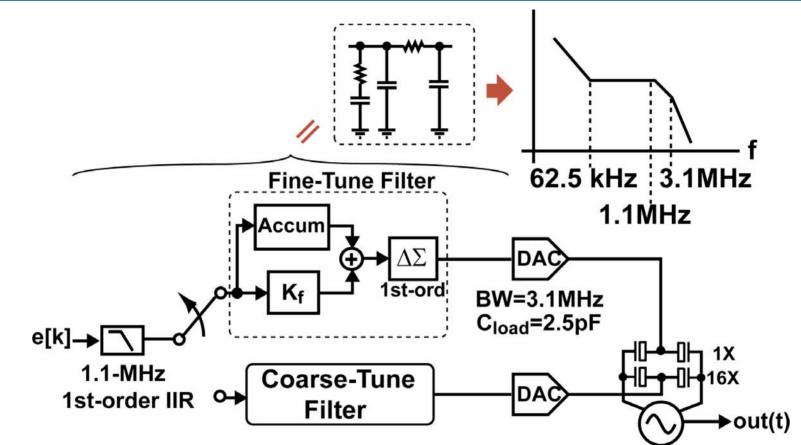

#### Fine-Path Loop Filter

Equivalent to an analog lead-lag filter

- Set zero (62.5kHz) and first pole (1.1MHz) digitally

- Set second pole (3.1MHz) by capacitor ratio

First-order ΔΣ reduces in-band quantization noise

#### Linearized Model of PLL Under Fine-Tune Operation

Standard lead-lag filter topology but implemented in digital domain

Consists of accumulator plus feedforward path

#### Same Technique Poses Problems for Coarse-Tune

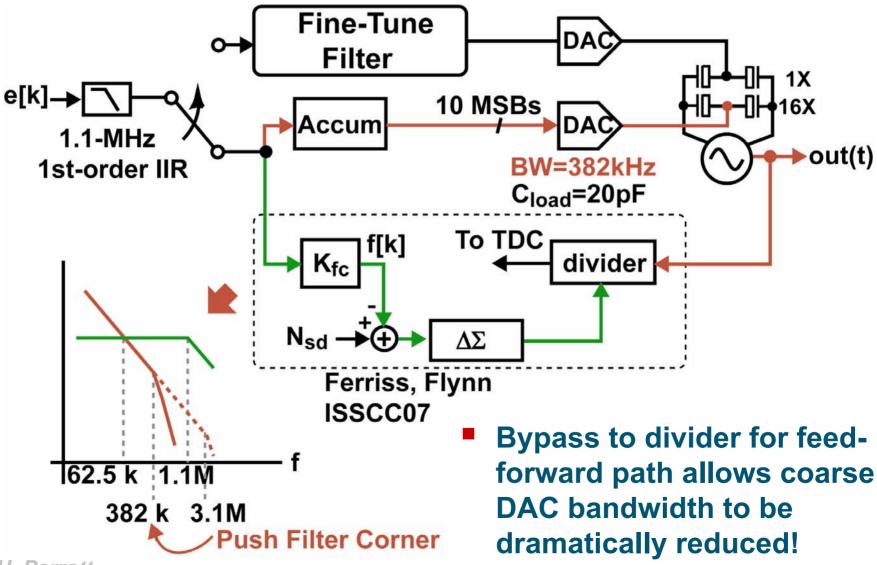

#### Fix: Leverage the Divider as a Signal Path

#### Linearized Model of PLL Under Coarse-Tune Operation

- Routing of signal path into Sigma-Delta controlling the divider yields a feedforward path

- Adds to accumulator path as both signals pass back through the divider

- Allows reduction of coarse DAC bandwidth

- Noise impact of coarse DAC on VCO is substantially lowered

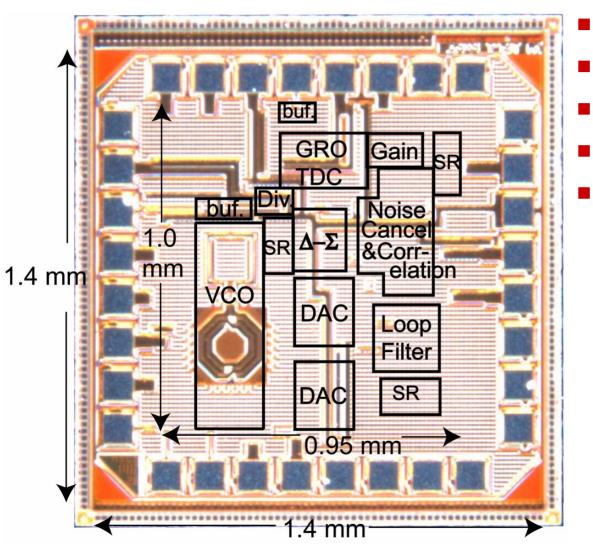

# **Die Photo of Prototype**

- 0.13-µm CMOS

- Active area: 0.95 mm<sup>2</sup>

- Chip area: 1.96 mm<sup>2</sup>

- V<sub>DD</sub>: 1.5V

- Current:

- 26mA (Core)

- 7mA (VCO output buffer at 1.1V)

- GRO-TDC: 2.3mA

- **157X252** um<sup>2</sup>

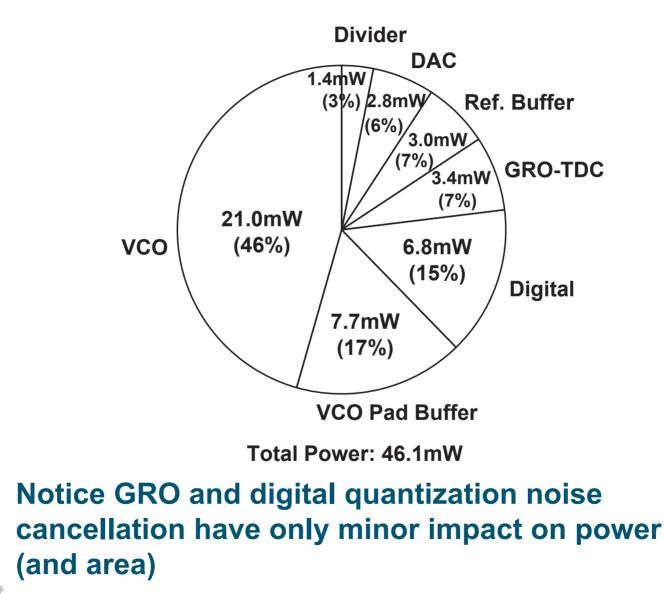

## **Power Distribution of Prototype IC**

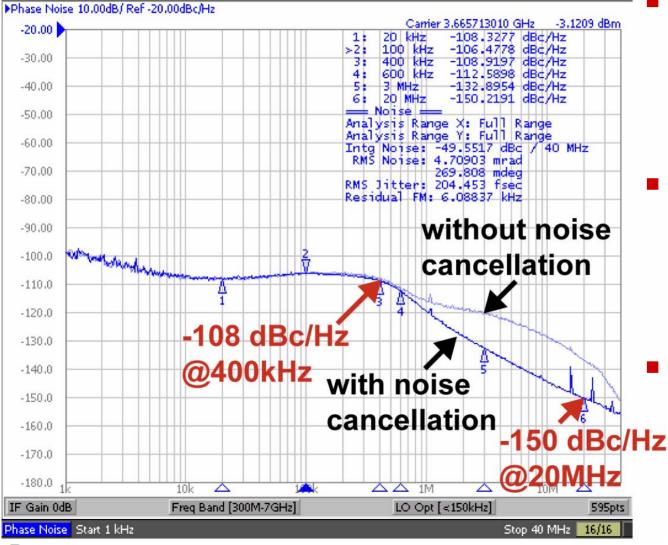

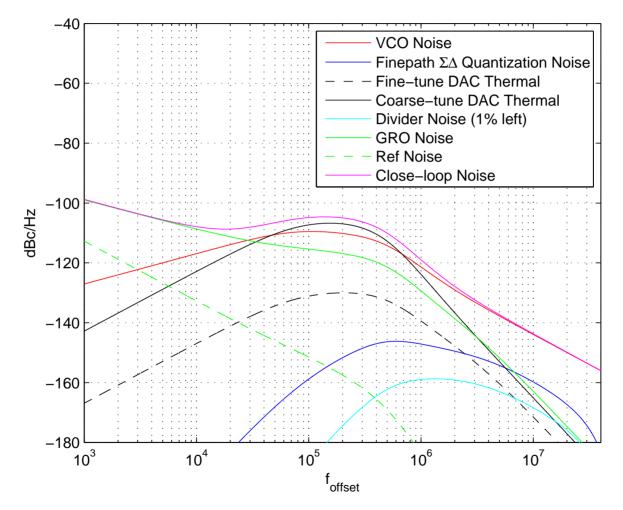

# Measured Phase Noise at 3.67GHz

#### Agilent E5052A Signal Source Analyzer

Suppresses quantization noise by more than 15 dB

- Achieves

204 fs

(0.27 degree)

integrated

noise (jitter)

- Reference spur: -65dBc

#### **Calculation of Phase Noise Components**

See wideband digital synthesizer tutorial available at http://www.cppsim.com M.H. Perrott

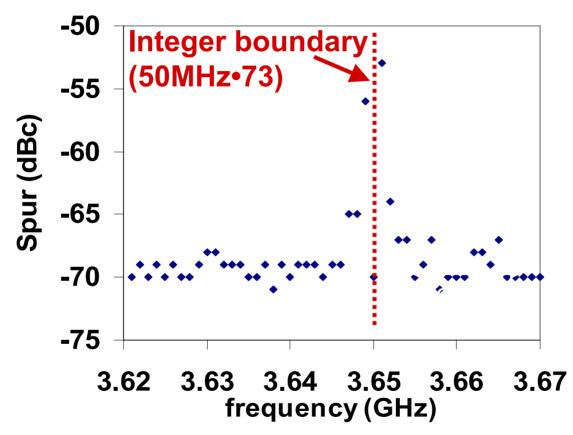

#### **Measured Worst Spurs over Fifty Channels**

- Tested from 3.620 GHz to 3.670 GHz at intervals of 1 MHz

- Worst spurs observed close to integer-N boundary (multiples of 50 MHz)

-42dBc worst spur observed at 400kHz offset from boundary M.H. Perrott

#### **Conclusions**

- Digital Phase-Locked Loops look extremely promising for future applications

- Very amenable to future CMOS processes

- Excellent performance can be achieved

- Analysis of digital PLLs is similar to analog PLLs

- PLL bandwidth is often chosen for best noise performance

- TDC (or Ref) noise dominates at low frequency offsets

- DCO noise dominates at high frequency offsets

- Behavioral simulation tools such as CppSim allow architectural investigation and validation of calculations

- TDC structures are an exciting research area

- Ideas from A-to-D conversion can be applied

# Innovation of future digital PLLs will involve joint circuit/algorithm development