## Fast Offset Compensation for a 10Gbps Limit Amplifier

by

Ethan A. Crain

Bachelor of Science in Electrical Engineering and Computer Science, Massachusetts Institute of Technology, December 1995

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Masters of Engineering in Electrical Engineering and Computer Science

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2004

© Massachusetts Institute of Technology 2004. All rights reserved.

Author\_\_\_\_\_

Department of Electrical Engineering and Computer Science May 15, 2004

Certified by\_\_\_\_\_

Michael H. Perrott Assistant Professor Thesis Supervisor

Accepted by\_\_\_\_\_

Arthur C. Smith Chairman, Department Committee on Graduate Students

#### Fast Offset Compensation for a 10Gbps Limit Amplifier

by

Ethan A. Crain

Submitted to the Department of Electrical Engineering and Computer Science on May 15, 2004, in partial fulfillment of the requirements for the degree of Masters of Engineering in Electrical Engineering and Computer Science

#### Abstract

A novel offset voltage compensation method is presented that significantly modifies the existing tradeoff between control loop bandwidth, and therefore total compensation time, and total output jitter. The proposed system achieves comparable output jitter performance to traditional approaches while significantly reducing the total compensation time by nearly three orders of magnitude.

Traditional offset compensation methods are based on simple offset measurement techniques that generally rely on passive compensation blocks and exhibit a direct inverse relationship between total compensation time and resulting output jitter. Therefore, current high-speed data-link systems suffer from extremely long offset compensation loop settling times in order to satisfy the strict protocol jitter specifications. In the proposed system, the new CMOS peak detector design is the enabling component that allows us break this relationship and achieve extremely fast settling behavior while preventing data dependence of the control signal.

Simulated results show that the implemented system can achieve output jitter performance similar to existing methods while dramatically improving the compensation time. Specifically, the proposed system can achieve less than 2pS of peak-to-peak jitter, or less than 700fS of RMS jitter, while reducing the total compensation time from roughly  $500\mu$ S to less than  $1\mu$ S. The system was implemented in National Semiconductor's CMOS9 0.18 $\mu$ m CMOS process. Packaged parts will be tested to verify agreement with simulated performance.

Thesis Supervisor: Michael H. Perrott Title: Assistant Professor "It is not the critic who counts: not the man who points out how the strong man stumbles or where the doer of deeds could have done better. The credit belongs to the man who is actually in the arena, whose face is marred by dust and sweat and blood, who strives valiantly, who errs and comes up short again and again, because there is no effort without error or shortcoming, but who knows the great enthusiasms, the great devotions, who spends himself for a worthy cause; who, at the best, knows, in the end, the triumph of high achievement, and who, at the worst, if he fails, at least he fails while daring greatly, so that his place shall never be with those cold and timid souls who knew neither victory nor defeat."

> Theodore Roosevelt University of Paris, Sorbonne April 23, 1910

## Acknowledgments

It was a significant decision to leave the work force, uproot my entire family from their home and friends and return to academia after an eight year hiatus. The path has not been without its trials and and I was tempted to give in on more than one occasion. That is why I feel extremely lucky to have an incredible group of friends, family, lab partners and mentors that helped me along the way. I owe a debt of gratitude to several people who made it possible for me to complete my Masters of Engineering thesis and dare to continue with my PhD.

First, I would like to thank my advisor, Michael Perrott, for taking a chance and believing in me. I have learned a tremendous amount in the last two years in both my work with you and in taking and TAing 6.976. I look forward to a white-knuckle PhD experience over the next couple of years.

I would also like to thank all of my lab partners, Charlotte Lau, Belal Helal, Shawn Kuo, Matt Park and Min Park, for keeping me sane and tolerating me for the last two years. I would especially like to thank Scott Meninger whose undying drive motivated me to keep going at my lowest points. In retrospect, the countless hours we spent slaving away on layout and debugging CAD tools was kind of fun in a sick and twisted way. I owe you a brew at the Thirsty after you tape out.

I would like to thank National Semiconductor for graciously fabricated my chip on their  $0.18\mu m$  CMOS9 process. I would not have been able to tape-out with out the help of Sangamesh Buddhiraju and Matthew Courcy who coordinated getting my chip onto the shuttle on time and ungrudgingly answered all of my questions.

Most importantly, I would like to thank Michelle, my wife, for daring to believe in me. Without your support this thesis would not have been possible. I love you and, in the words of a man much wiser than I, I owe you big time. My two sons, Jacob and Samuel, have been extremely patient and understanding. Some day I hope that you understand why I made the decision to come back to school and forgive me for not being around as much as you would like. I owe you a quite a few play dates at the park.

I would like to thank my parents, Stephen and Pauline, for pointing me in the right direction at an early age. I hope that we get to spend some time visiting my brothers Brad, Geoffrey and Justin, my sister Michelle and their families when I get a little down time this summer.

Finally, I would like to thank Fairchild Semiconductor for their generous financial support that they provided in my first year of graduate school.

# Contents

| 1        | Intr | oducti           | ion                                                           | 19 |

|----------|------|------------------|---------------------------------------------------------------|----|

|          | 1.1  | Backg            | round                                                         | 20 |

|          | 1.2  | Motiva           | ation                                                         | 22 |

|          |      | 1.2.1            | Review of Offset Voltage                                      | 22 |

|          |      | 1.2.2            | Impact of Offset Voltage on Amplifiers                        | 23 |

|          | 1.3  | Prior            | Offset Compensation Approaches                                | 23 |

|          |      | 1.3.1            | Sampled Offset Compensation                                   | 23 |

|          |      | 1.3.2            | Low-Pass Filter Compensation                                  | 24 |

|          |      | 1.3.3            | Other Approaches                                              | 25 |

|          | 1.4  | Propo            | sed Approach and Contribution                                 | 26 |

|          | 1.5  | Thesis           | Organization                                                  | 26 |

| <b>2</b> | Pro  | $\mathbf{posed}$ | Approach                                                      | 29 |

|          | 2.1  | Measu            | ring Offset Voltage                                           | 29 |

|          |      | 2.1.1            | Extracting the Offset Voltage with Min/Max Detectors          | 29 |

|          |      | 2.1.2            | Issues with Sensing Offset with Min/Max Detectors $\hdots$    | 30 |

|          |      | 2.1.3            | Extracting Offset with Simple Max Detectors                   | 31 |

|          |      | 2.1.4            | Issues with Sensing Output Referred Offset with Max Detectors | 32 |

|          |      | 2.1.5            | Final Peak Detector Design                                    | 33 |

|          | 2.2  | Summ             | ary                                                           | 34 |

| 3        | System Modeling |                                                                    | 37 |

|----------|-----------------|--------------------------------------------------------------------|----|

|          | 3.1             | System Level Implementation                                        | 37 |

|          | 3.2             | Linear System Modeling                                             | 39 |

|          |                 | 3.2.1 Modeling System Response with PLL Design Assistant $\ldots$  | 42 |

|          |                 | 3.2.2 Modeling the Impact of System Parameter Variation on Stabil- |    |

|          |                 | ity and Compensation Time                                          | 44 |

|          | 3.3             | Summary                                                            | 44 |

| 4        | Nu              | merical Design of High Speed Differential Amplifiers               | 47 |

|          | 4.1             | Methodology                                                        | 47 |

|          | 4.2             | Proposed Approach                                                  | 49 |

|          |                 | 4.2.1 Derivation of Gain/Swing Constraint Formulation              | 50 |

|          |                 | 4.2.2 Derivation of Gain-Bandwidth Tradeoff                        | 50 |

|          | 4.3             | Intuitive Insights from Method                                     | 51 |

|          | 4.4             | Results                                                            | 52 |

|          | 4.5             | Application to SCL Digital Circuits                                | 53 |

|          | 4.6             | Summary                                                            | 54 |

| <b>5</b> | Cire            | cuit Design of Systems Blocks                                      | 55 |

|          | 5.1             | High Speed Limit Amplifier                                         | 55 |

|          |                 | 5.1.1 Determining Optimal Number of Stages                         | 56 |

|          |                 | 5.1.2 Bandwidth Extension Techniques                               | 62 |

|          |                 | 5.1.3 Final Amplifier Design                                       | 63 |

|          | 5.2             | Peak Detector                                                      | 64 |

|          | 5.3             | Integrator                                                         | 67 |

|          | 5.4             | Output Buffer                                                      | 74 |

|          | 5.5             | Comparator and Logic                                               | 75 |

|          | 5.6             | ESD                                                                | 78 |

|   | 5.7                  | Summary                                  | 78 |

|---|----------------------|------------------------------------------|----|

| 6 | $\operatorname{Res}$ | ults                                     | 79 |

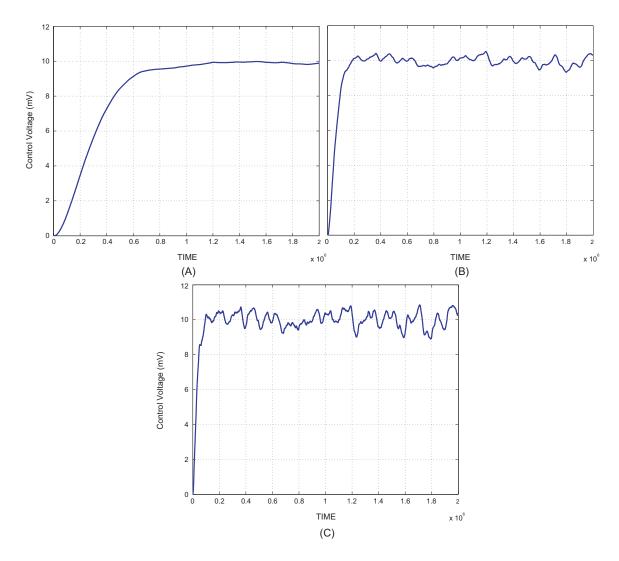

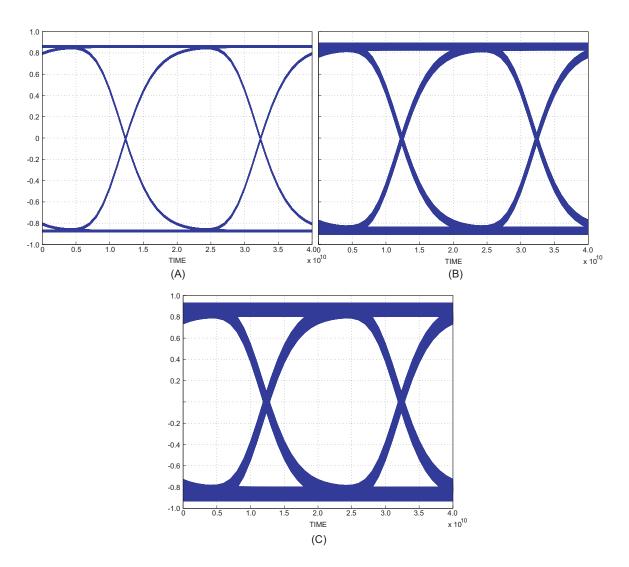

|   | 6.1                  | CppSim Modeling and Simulation Results   | 79 |

|   |                      | 6.1.1 Limit Amplifier                    | 79 |

|   |                      | 6.1.2 Peak Detector                      | 80 |

|   |                      | 6.1.3 Integrator                         | 80 |

|   |                      | 6.1.4 Control Logic                      | 81 |

|   | 6.2                  | CppSim Simulation Results                | 81 |

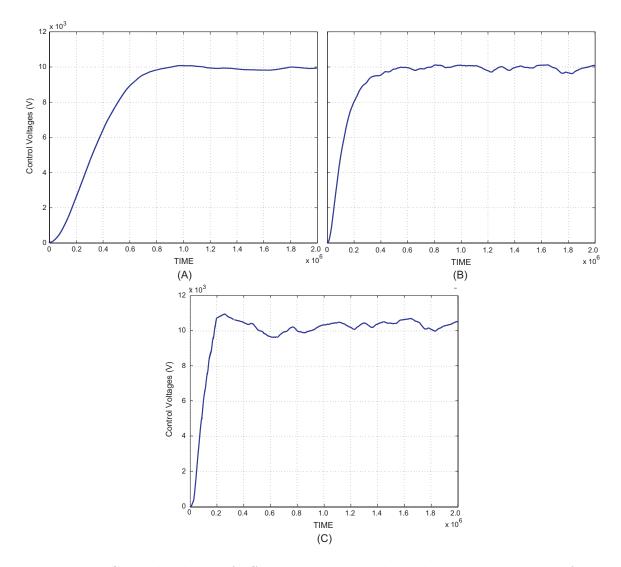

|   | 6.3                  | Hspice Simulation Results                | 81 |

|   | 6.4                  | Summary                                  | 82 |

| 7 | Lay                  | out                                      | 87 |

|   | 7.1                  | Peak Detector                            | 87 |

|   | 7.2                  | Integrator                               | 87 |

|   | 7.3                  | High Speed Limit Amplifier               | 88 |

|   | 7.4                  | Output Buffer                            | 89 |

|   | 7.5                  | Top Level                                | 90 |

|   | 7.6                  | Summary                                  | 91 |

| 8 | Cor                  | clusions and Future Work                 | 93 |

|   | 8.1                  | Contributions                            | 93 |

|   | 8.2                  | Future Work                              | 94 |

| A | Der                  | ivation of Input Referred Offset Voltage | 95 |

|   |                      | A.0.1 Square-Law Operation               | 96 |

|   |                      | A.0.2 Velocity Saturation                | 97 |

| в | Cire                 | cuit Design Details                      | 99 |

|   | B.1                  | ESD Design                               | 99 |

| С            | Cpp | Sim Code                                   | 101 |

|--------------|-----|--------------------------------------------|-----|

|              | C.1 | Limit Amplifier Code                       | 101 |

|              | C.2 | Peak Detector Code                         | 102 |

|              | C.3 | Integrator Code                            | 102 |

|              |     |                                            |     |

| D            | Opt | imal Gain/Stage for Maximum Bandwidth      | 103 |

|              |     | D.0.1 Determining Optimal Number of Stages | 103 |

|              |     |                                            |     |

| $\mathbf{E}$ | Mat | lab Amplifier Script                       | 107 |

|              | E.1 | Script for Fixed Bandwidth                 | 107 |

|              | E.2 | Script for Fixed Power Dissipation         | 112 |

# List of Figures

| 1-1 | Block Diagram of High-Speed Data Link System                          |    |

|-----|-----------------------------------------------------------------------|----|

| 1-2 | High-Speed, Multi-Stage Limit Amplifier                               |    |

| 1-3 | Implementation of Each Stage in Limit Amplifier                       | 21 |

| 1-4 | LPF to Extract Output Referred Offset in High-Speed Data Link Systems | 24 |

| 2-1 | Measuring Output Referred Offset Voltage Using Minimum and Max-       |    |

|     | imum Detectors                                                        | 30 |

| 2-2 | Traditional Implementations for Minimum and Maximum Detectors .       | 30 |

| 2-3 | Influence of Symbol Period on Droop of Simple Peak Detector $\ldots$  | 32 |

| 2-4 | Measuring Output Referred Offset Voltage Using Maximum Detectors      |    |

|     | Only                                                                  | 32 |

| 2-5 | Schematic of Typical CMOS Maximum Detector                            | 33 |

| 2-6 | Schematic of Proposed Peak Detector with Reduced Droop                | 34 |

| 2-7 | Comparison of Influence of Symbol Period on Droop of Simple Peak      |    |

|     | Detector vs Proposed Peak Detector Design                             | 34 |

| 3-1 | System Level of Limit Amplifier with Offset Compensation              | 38 |

| 3-2 | Typical Transfer Function for Limit Amplifier Cell                    | 38 |

| 3-3 | Complete System Showing Multiple Control Loops and Logic              | 39 |

| 3-4 | Linear Model of Limit Amplifier with Offset Compensation              | 41 |

| 3-5 | Bode Plot Showing Stability Degradation with Increasing Gain          | 42 |

| 3-6  | Root Locus Plot of $G(s)$ Showing Necessary Condition for Stability . 43    |    |

|------|-----------------------------------------------------------------------------|----|

| 3-7  | PLL Design Assistant Graphical Interface                                    |    |

| 3-8  | Step Response of System Designed with PLL Design Assistant 44               |    |

| 3-9  | PLL Design Assistant Graphical Interface                                    | 45 |

| 3-10 | Impact of $\pm 20\%$ Variation in Loop Gain and Dominant Pole Location      |    |

|      | on the Step Response of the System                                          | 45 |

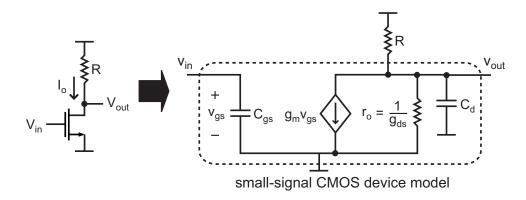

| 4-1  | Differential amplifier used in calculations                                 | 48 |

| 4-2  | Small signal model for amplifier                                            | 49 |

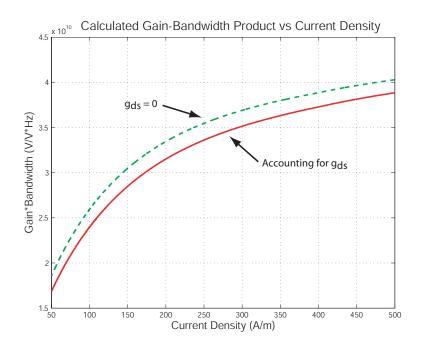

| 4-3  | Calculated Gain-Bandwidth product vs $I_{den}$                              | 52 |

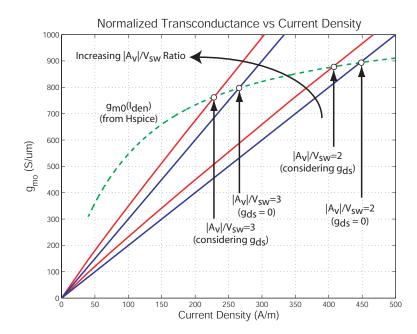

| 4-4  | Current density settings versus gain/swing                                  | 53 |

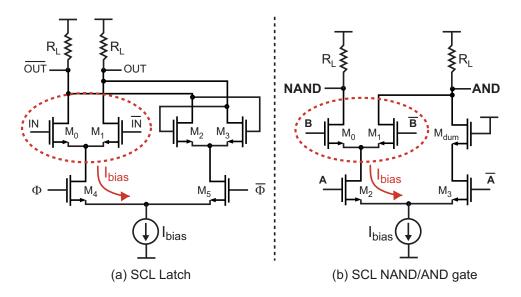

| 4-5  | Digital high speed circuits                                                 | 54 |

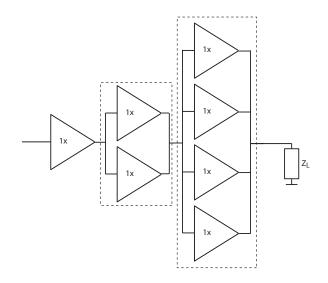

| 5-1  | High-Speed, Multi-Stage Limit Amplifier                                     | 55 |

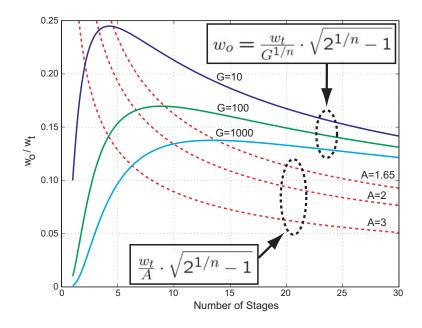

| 5-2  | Number of Stages vs Total Bandwidth: Normalized Total Bandwidth             |    |

|      | vs Number of Stages for $G^{1/n} = A = 1.65$ , 2.0 and 3.0 and Total Gains, |    |

|      | G, of 10, 100 and 1000                                                      | 57 |

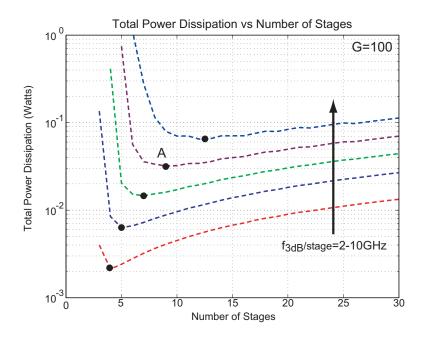

| 5-3  | Total Power Dissipation of Limit Amplifier for a Total Gain of 100 and      |    |

|      | Bandwidths/Stage from 2-10GHz                                               | 59 |

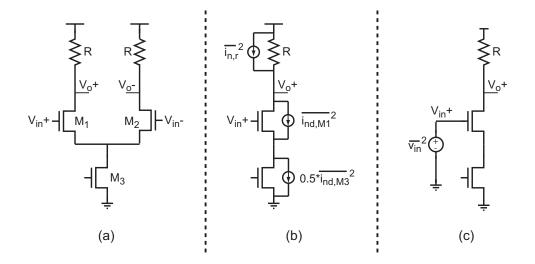

| 5-4  | (a) Full Resistive-Loaded Differential Amplifier (b) Half-Circuit with      |    |

|      | Noise Sources Added (c) Half-Circuit with Noise Source Referred to          |    |

|      | Input                                                                       | 60 |

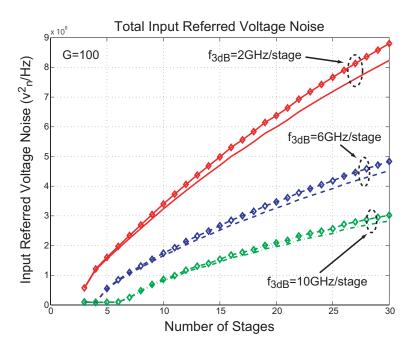

| 5-5  | Total Input Referred Voltage Noise Versus Number of Amplifier Stages        |    |

|      | for a Fixed Total Gain                                                      | 61 |

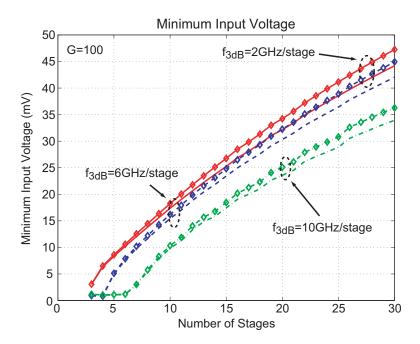

| 5-6  | Minimum Input Voltage Versus Number of Amplifier Stages for a Fixed         |    |

|      | Total Gain                                                                  | 62 |

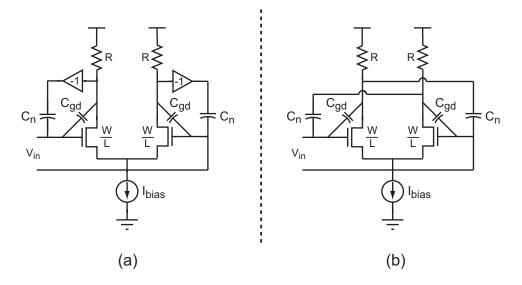

| 5-7  | Limit Amplifier Stage with Neutralization Capacitors                        | 63 |

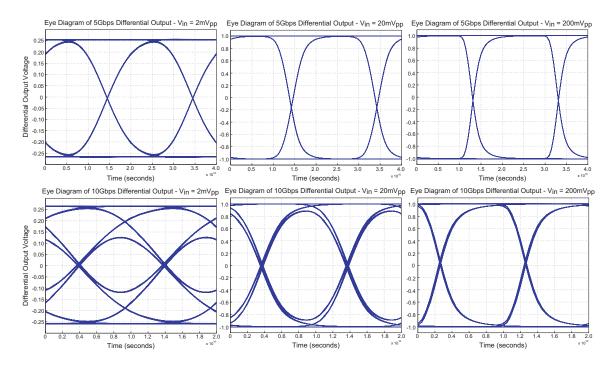

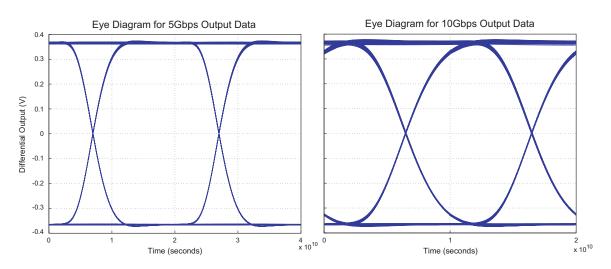

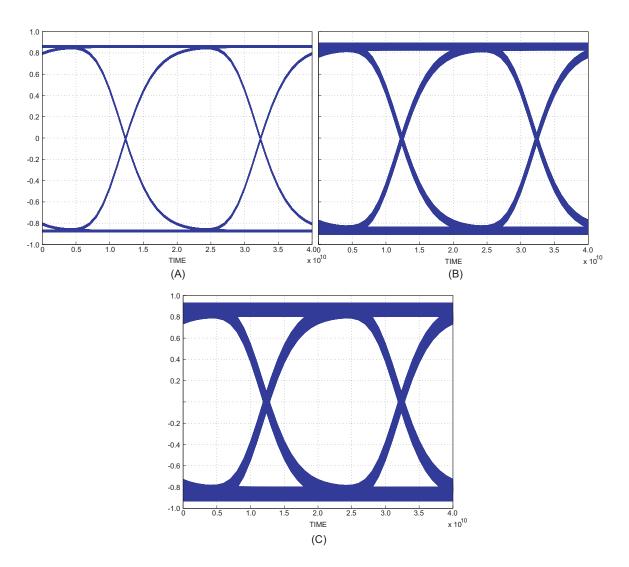

| 5-8  | Eye Diagrams for the Limit Amplifier at Data Rates of 5Gbps and                                          |    |  |

|------|----------------------------------------------------------------------------------------------------------|----|--|

|      | $10\mathrm{Gbps}$ and input amplitudes of $2\mathrm{mV},20\mathrm{mV}$ and $200\mathrm{mV}$ peak-to-peak | 65 |  |

| 5-9  | Simplified Schematic of Fully Differential Peak Detector                                                 | 66 |  |

| 5-10 | Basic Differential RC Integrator                                                                         | 67 |  |

| 5-11 | Simplified Schematic of Differential $g_m$ C Integrator                                                  | 68 |  |

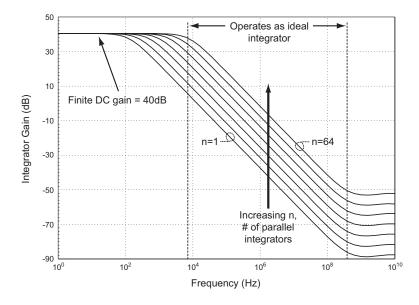

| 5-12 | Bode Plot of Modified Open-Loop Parameter $A(s)$                                                         | 70 |  |

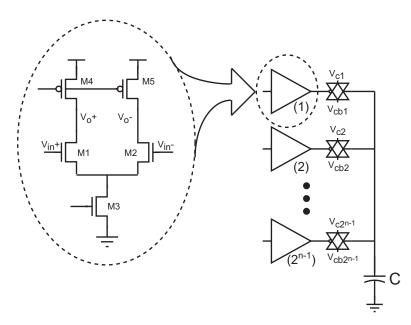

| 5-13 | Schematic showing how integrator array is configured                                                     | 71 |  |

| 5-14 | Bode Plot of integrator demonstrate how transfer function varies with                                    |    |  |

|      | n, the number of parallel integrator cells $\ldots \ldots \ldots \ldots \ldots \ldots$                   | 72 |  |

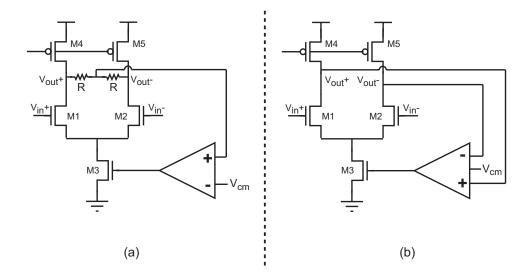

| 5-15 | (a) CMFB with Resistive Output Common-Mode Level Sensing, (b)                                            |    |  |

|      | CMFB Using Differential Amplifier to Sense Output Common-Mode                                            |    |  |

|      | Level                                                                                                    | 73 |  |

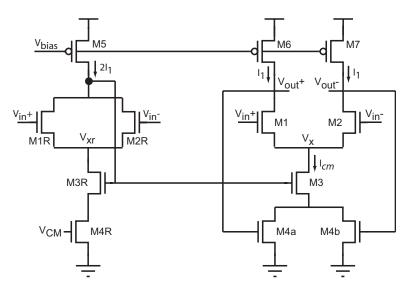

| 5-16 | Simplified Schematic of Integrator Showing Biasing and CMFB $\ . \ .$ .                                  | 73 |  |

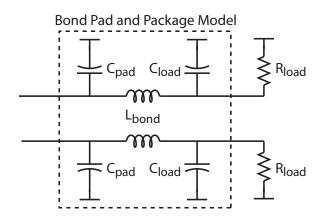

| 5-17 | Differential Package Model Showing the Bond Pad and Package Ca-                                          |    |  |

|      | pacitance and the Bond Wire Inductance                                                                   | 74 |  |

| 5-18 | Final Output Buffer Design                                                                               | 75 |  |

| 5-19 | Eye Diagram at Output of Output Buffer (a) 5Gbps, (b) 10Gbps                                             | 75 |  |

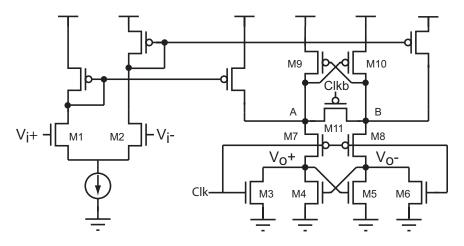

| 5-20 | Typical Implementation of Clocked Comparator                                                             | 76 |  |

| 5-21 | Implementation of Comparator in Windowing Block                                                          | 77 |  |

| 6-1  | 3rd Order Polynomial Fit to Limit Amplifier Transfer Function Mea-                                       |    |  |

|      | sured in Hspice                                                                                          | 80 |  |

| 6-2  | Control voltage of offset compensation loop during compensation from                                     |    |  |

|      | CppSim: (A) 1MHz bandwidth, (B) 5MHz bandwidth, (C) 10 MHz                                               |    |  |

|      | Bandwidth                                                                                                | 82 |  |

| 6-3  | Eye diagram of limit amplifier output after compensation from CppSim                                     | 83 |  |

| 6-4 | Control voltage of offset compensation loop during compensation from   |     |  |

|-----|------------------------------------------------------------------------|-----|--|

|     | Hspice: (A) 1MHz bandwidth, (B) 5MHz bandwidth, (C) 10 MHz             |     |  |

|     | Bandwidth                                                              | 84  |  |

| 6-5 | Eye diagram of limit amplifier output after compensation from Hspice   | 85  |  |

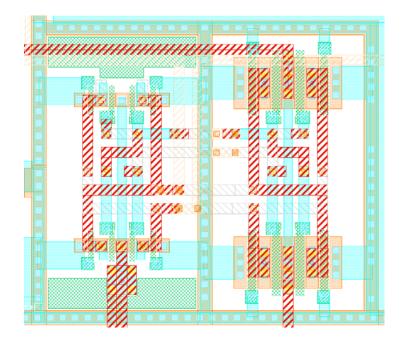

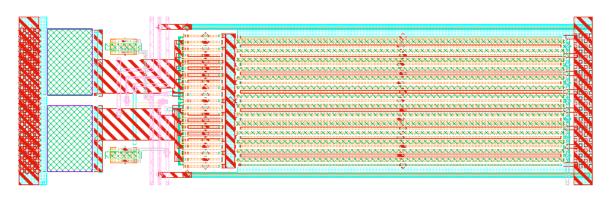

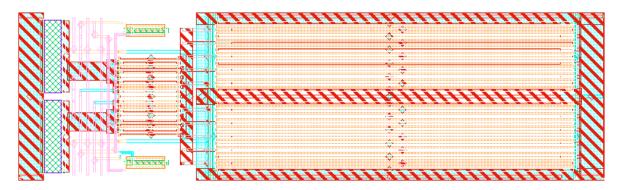

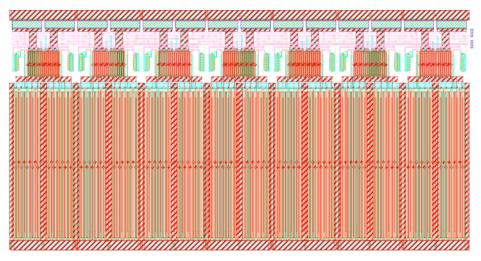

| 7-1 | Detail of Peak Detector Cell Showing Common-Centroid Layout and        |     |  |

|     | Dummy Devices                                                          | 88  |  |

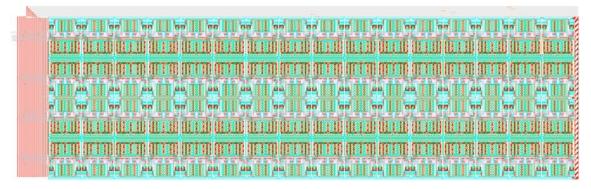

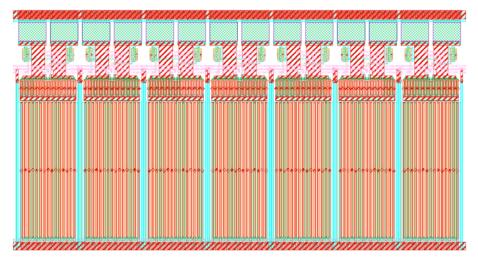

| 7-2 | Layout of Base Integrator Cell                                         | 89  |  |

| 7-3 | Layout of Integrator Array                                             | 89  |  |

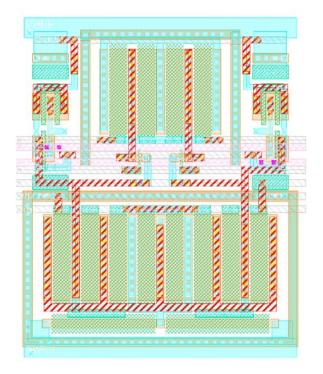

| 7-4 | Layout of Limit Amplifier Stage                                        | 90  |  |

| 7-5 | Layout of Limit Amplifier Top Level                                    | 90  |  |

| 7-6 | Layout of Output Buffer Stage                                          | 91  |  |

| 7-7 | Layout of Output Buffer Top Level                                      | 91  |  |

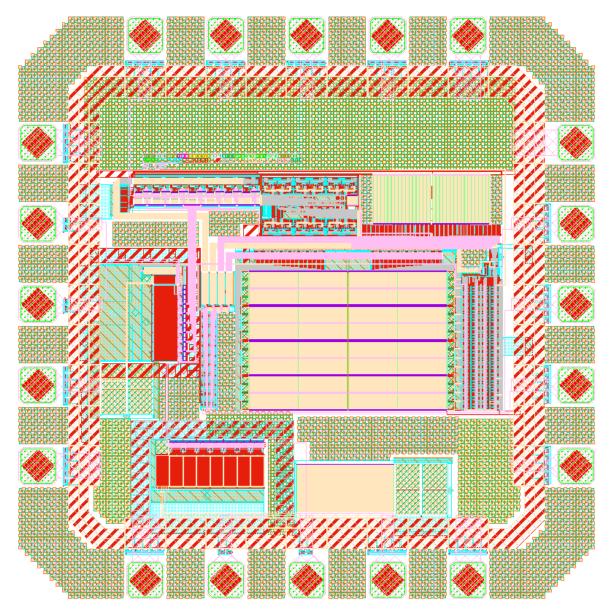

| 7-8 | Layout of Chip Top Level                                               | 92  |  |

| A-1 | Implementation of Each Stage in Limit Amplifier                        | 95  |  |

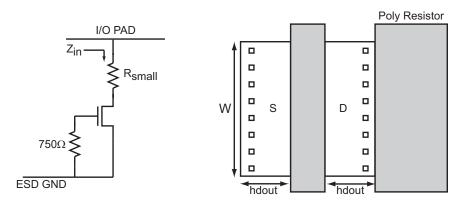

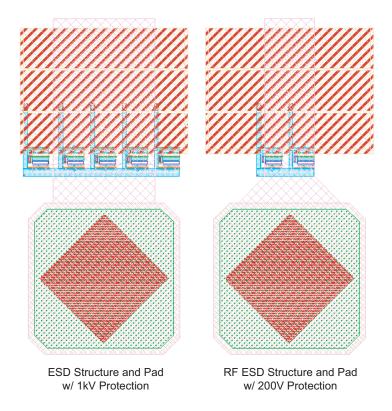

| B-1 | Simplified schematic of ESD circuitry used on all pads                 | 99  |  |

| B-2 | Layouts for the two pads with ESD structures $\ . \ . \ . \ . \ . \ .$ | 100 |  |

| D-1 | High-Speed, Multi-Stage Limit Amplifier                                | 103 |  |

# List of Tables

| 1.1 | Typical vs Goal Performance Specifications for Offset Compensation . | 26 |

|-----|----------------------------------------------------------------------|----|

| 4.1 | Calculated vs simulated amplifier performance                        | 52 |

| 5.1 | Simulated Hysteresis vs Process and Temperature Corner               | 77 |

## Chapter 1

## Introduction

In today's information age there is an ever increasing demand for products that deliver higher performance, lower power dissipation and smaller form factor than existing designs. New products that improve in these three areas will enable the continued exponential growth of the worldwide communication infrastructure. Ultimately, a combination of novel architectural and circuit techniques need to be developed to achieve this end.

Offset compensation is important for aggressive high speed design to achieve high input sensitivity and low DC offset. In traditional offset compensation implementations the data dependence of the control signal is proportional to the compensation loop bandwidth. As a result of this limitation, current approaches suffer from long compensation times and require expensive off-chip components to minimize data-dependent jitter and to meet protocol (i.e. SONET/SDH) jitter specifications. Manipulation of fundamental characteristics of the differential architecture allow us to modify this relationship in the proposed approach. The goal of this thesis is to develop a broadband limit amplifier with dynamic, fully integrated, continuous-time DC offset cancellation that achieves sub-1 $\mu$ S compensation times while providing a low jitter, constant amplitude output. The limit amplifier will be used as the main amplifier in an optical network receiver. The chip has been implemented in National Semiconductor's CMOS9 0.18 $\mu$ m CMOS process.

Additionally, a simple numerical procedure is introduced that enables straightforward design of high speed, resistor loaded, differential amplifiers in modern CMOS processes. The design procedure is beneficial because the device characteristics of modern CMOS processes dramatically depart from traditional square law characteristics. The analytical form of the procedure allows for an intuitive perspective of the varying gain-bandwidth product for such amplifiers. Calculations based on the method are compared to Hspice simulated results based on a National Semiconductor's 0.18u CMOS process. Application of the design methodology to the design of high speed, source-coupled logic (SCL) gates and latches is also discussed.

### 1.1 Background

One well established industry standard for broadband optical fiber networks known as SONET, or Synchronous Optical NETwork, is defined for various data speeds. Operating at a data rate of 10Gbps, the OC-192 SONET standard allows for very high data transfer rates on optical fiber cable over long distances. One obstacle to achieving the desired performance is DC offset in the data link. The offset can be introduced by the transmitter, the transmit path or the circuit components in the front-end receiver. The desire to reduce the cost structure and improve the efficiency of these networks will increase the demand for quick power-up and switching between multiple incoming links. This demand will drive the need for fast DC offset compensation.

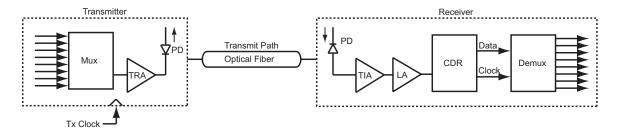

Figure 1-1 exhibits a block diagram of a modern optical-link system. At the transmit end of the fiber cable, a laser driver feeds a synchronous, Non-Return to Zero (NRZ) data stream into the cable, which can range in length from tens to thousands of kilometers. Sending distinct clock and data signals would require separate, dedicated cables and would be prohibitively expensive. Therefore, a single serial data stream is transmitted with the clock encoded in the data transitions. At the receiver end of the cable an avalanche photo-diode drives a Transimpedance Amplifier (TIA) that translates the current signal to a voltage signal. The output of the TIA then feeds the main amplifier, which is the focus of this thesis. The main amplifier must amplify this small voltage signal to a large enough level so that the clock and data recovery (CDR) circuitry can operate reliably. The purpose of the CDR is to extract the clock signal from the data stream and re-time the data to the new, synchronized clock signal.

Figure 1-1: Block Diagram of High-Speed Data Link System

The overall design goal of the main amplifier is to increase the signal strength without degrading the SNR achieved by the system front-end. Additionally, the amplifier must provide a low jitter, constant amplitude input to the CDR. There are two main architectures that can be used to implement the amplifier, namely an Automatic Gain Control (AGC) amplifier or a Limit Amplifier (LA). As the name suggests, the AGC amplifier dynamically adjusts its gain depending on the input amplitude to achieve a constant amplitude output signal. In contrast, the limit amplifier achieves the same effect by forcing the output to saturate at a known amplitude for input signals greater than some predetermined minimum amplitude. The limit amplifier design was selected for this work because it is more amenable to high-speed operation.

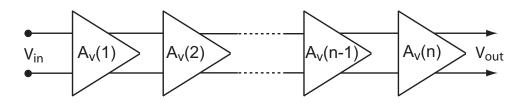

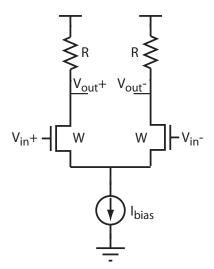

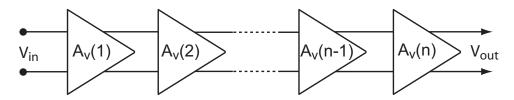

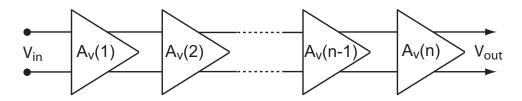

The key advantages of the limiting amplifier over the AGC are higher operating speed and lower implementation complexity. AGCs will exhibit inferior highfrequency characteristics compared to limit amplifiers because of the increased capacitive loading of the sense and feedback circuitry. Also, the added feedback network, for gain control, increases the design complexity. Therefore, the limiting amplifier topology was used in this thesis. A limit amplifier can be implemented as a cascade of resistively loaded differential pair amplifiers, as shown in Figure 1-2. Each of the amplifier blocks is implemented as differential pairs, as shown in Figure 1-3.

Figure 1-2: High-Speed, Multi-Stage Limit Amplifier

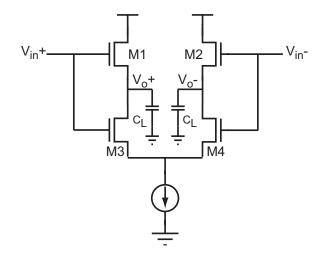

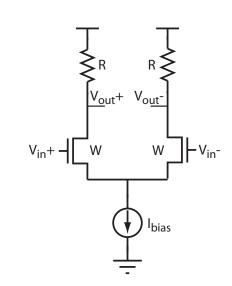

Figure 1-3: Implementation of Each Stage in Limit Amplifier

Cost is the fundamental driving force behind process selection for modern day integrated circuits. CMOS has become the process of choice compared to more specialized III-IV processes like SiGe, GaAs and InP due to the immense inertia behind process development in the PC market. However, this economic advantage does not come without added design challenges. CMOS presents its own unique problems for high speed design due to its lower  $f_t$  and higher 1/f noise corner compared to the afore mentioned processes. Despite these challenges, CMOS is the preferred technology due to its low cost, high integration density and fast paced technology development driven by Moore's Law.

### 1.2 Motivation

#### 1.2.1 Review of Offset Voltage

As mentioned earlier, the data-link network suffers from two main sources of DC offset. The first source of offset is the received signal. The circuit components of the receiver are the other source of offset. The following section will examine the origin of these two sources of offset and the impact of the offset on the system.

The offset introduced by the incoming signal originates at the transmitter and is due to the power of the incoming signal. When the receiver initially powers up, the received signal power may introduce a DC offset in the receiver. Additionally, the magnitude of the offset can change when switching from one transmit path to another. Different power levels between the two transmit paths, caused by different output powers of the two transmitters or different losses in the transmit paths, will result in a change in the DC voltage offset of the receiver.

The main amplifier itself may also introduce a finite DC offset component due to mismatches in the differential paths. To understand the origin of the offset voltage, consider the resistively loaded differential pair shown in Figure 1-3. Assuming  $V_{in} = 0$ and perfect symmetry,  $V_{out} = 0$ . However, this assumption is violated in practice due to device mismatches in transistor physical dimensions, threshold voltages and resistor values so that  $V_{out} \neq 0$ . The output referred offset voltage is defined as the voltage that exists at the output with  $V_{in} = 0$ . By convention, this voltage is referred to the input and the offset voltage is therefore the voltage that must be applied to the input to force  $V_{out} = 0$ . The input referred offset is related to the output referred offset voltage by  $|V_{os,in}| = |\frac{V_{os,out}}{A_v}|$ , where  $A_v$  is the gain of the amplifier.

It is beneficial to develop an expression for the offset voltage in terms of the circuit parameters to determine how we, as the designer, can minimize it. Assuming that the input devices operate in velocity saturation, the final expression for the input referred offset voltage is:

$$V_{os,in}^2 = (V_{GS} - V_{TH})^2 \cdot \left[ \left( \frac{\Delta W}{W} \right)^2 + \left( \frac{\Delta R}{R} \right)^2 \right] + \Delta V_{TH}^2$$

(1.1)

where  $(\Delta W/W)$ ,  $(\Delta R/R)$  and  $(\Delta V_{TH}/V_{TH})$  are the normalized variation in the transistor width, load resistance and transistor threshold voltage, respectively, of the amplifier. The reader is invited to refer to Appendix A for the full development. The resulting equation is similar to the result found in [1], where square-law operation was assumed. The exception is that a scaling in the magnitude of the over-drive term and no direct dependence on device length, L. The offset is indirectly dependent on L through the  $V_{TH}^2$  term.

By examining this result some useful insights can be obtained. First, the offset voltage is dependent on transistor length mismatches through the dependence on threshold mismatches. Second, this analysis shows that threshold voltage mismatches are directly referred to the input and that mismatches in transistor width and load resistance are scaled by the transistor over-drive. Therefore, to minimize offset voltage, the transistor over-drives should be minimized by either reducing the bias current or by increasing the device widths. Reducing the bias current is only appropriate in low power (i.e. low-speed) designs. As will be shown in Chapter 4, the transistor widths and load resistance are not free variables when designing resistively loaded, differential amplifiers. The device dimensions and bias conditions are uniquely determined when the gain, output swing and either bandwidth or power are specified. Additionally, appropriate layout matching techniques such as common-centroid layout and using dummy devices/stripes to minimize device mismatch should be incorporated where appropriate. Unfortunately, as shown in Equation 1.1, the offset voltage of the amplifier can not be reduced to zero even if the utmost care is taken in the design and layout. In the next section we will explore the impact of DC offsets on the performance of the amplifier.

#### **1.2.2** Impact of Offset Voltage on Amplifiers

Both the undesired input-referred offset and the desired input signal experience the large gain of the limit amplifier, which is usually on the order of 40dB to 60dB. Typical values of input-referred offset voltage can range from 1mV to 10mV since the high-speed amplifier stages are designed for maximum bandwidth at the expense of matching and offset issues. The input-referred offset can be comparable in magnitude to the input signal levels for high-speed optical receivers. For this reason, the offset voltage can decrease sensitivity to incoming signals or, even worse, drive the later stages into nonlinear operation and cause the outputs to saturate. In extreme cases, the offset can be large enough to block the desired signal. For these reasons, some form of offset compensation is required in modern, high-speed data-link systems.

## **1.3** Prior Offset Compensation Approaches

Several existing offset compensation techniques can be found in the literature. The existing approaches generally fall into one of two categories: active sampled systems or passive continuous time systems. We will explore the most significant methods in this section. Two important characteristics of each design are the compensation time and the data dependent output jitter. Long compensation times lead to loss of data and decrease system efficiency. One source of jitter in the output signal is data dependence of the offset compensation control signal. Unless the measured offset is sufficiently filtered in this method, the proportional control signal will lead to increased output jitter. All of the system discussed below exhibit a direct relationship between compensation time and output jitter.

#### **1.3.1** Sampled Offset Compensation

The three most common offset compensation techniques that fall into the sampled system classification are auto-zeroing, correlated double sampling and chopper stabilization [2]. The basic principle behind auto-zeroing and correlated double sampling is to sample the undesired offset that exists in the system on one clock phase and to subtract it from the desired signal on the following clock phase. By design, both of these techniques require a clock and a sampling phase to measure the offset in the system, fundamentally limiting the maximum input data rate to half the sampling rate. Additionally, each of these techniques require sampling capacitors in the data path which can be quite large if designed for minimal noise. On the other hand, chopper stabilization achieves the same result by operating in the frequency domain. Compensation is performed by modulating the desired signal to a higher frequency, where the undesired offset and noise signals do not exist, performing the amplification on the modulated signal and finally demodulating the amplified signal back to baseband. Chopper-stabilization methods are fundamentally limited to low-speed applications because the residual offset, or the offset remaining after compensation, is proportional to the sampling rate. If the sampling rate is set too high, the residual offset will increase. Also, the forward path gain can be attenuated and the noise floor will increase due to the aliasing of the wide-band noise into the frequency band of interest. Ultimately, none of these techniques are amenable to high-speed, continuous-time systems.

#### **1.3.2** Low-Pass Filter Compensation

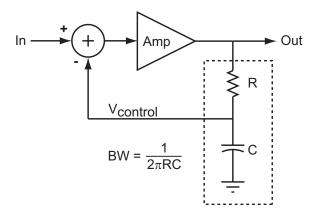

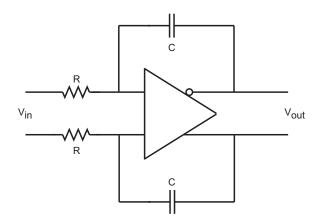

By far, the most common technique for offset compensation in continuous time, highspeed, broadband systems is to use a low-pass filter in a feedback configuration [3, 4, 5], as shown in Figure 1-4. The bandwidth of the filter must be set sufficiently low to ensure stability of the overall system and to ensure that there is minimal data dependence of the control loop.

Figure 1-4: LPF to Extract Output Referred Offset in High-Speed Data Link Systems

Due to the requirement for such a low loop bandwidth, this design has two significant disadvantages. First, the very small loop bandwidth translates to a very large time constant for the loop dynamics which results in very long compensation times [6, 7]. Long compensation times will become a significant issue as emerging standards such as Optical Time-Division Multiplexing (OTDM) [8] and Dense-Wave Division Multiplexing (DWDM) [9] take hold in commercial applications. Second, from the viewpoint of cost and ease of integration, the small bandwidth requirement results in large component values that are not economically feasible to implement on chip. Specifically capacitor values on the order of 10's of  $\mu$ F are required which would consume considerable silicon area if implemented on chip. The result is the need for expensive off-chip components.

#### **1.3.3** Other Approaches

One of the earliest forms of offset compensation in the literature uses Minimum Mean-Square Estimation (MMSE) [10, 11]. Similar to Chopper Stabilization, MMSE performs the offset compensation in the frequency domain using adaptive equalizers. The equalizers, which are slowly time-varying linear filters, will insert a null in the transfer function at DC to compensate for DC offsets. One issue with this approach is that the magnitude of residual offset is proportional to both the number of filter taps and the magnitude of the uncompensated offset of the system. Therefore, low residual DC offset requires high equalizer complexity and a small input referred offset. As CMOS processes continue to scale the increased digital complexity required to implement the higher order filters will become less of an issue and this approach may become more feasible.

Another solution, implemented in a silicon bipolar process, uses peak detectors to measure the output referred DC offset (drift) of the main amplifier [11]. The output of the peak detector is low-pass filtered to reduce the data dependence of the control signal. Finally, the output of the low-pass filter feeds the input stage to perform the compensation. Similar to the low-pass filter approach, the data dependence of the control signal is proportional to the control loop bandwidth. To minimize the output jitter this design also suffers from very long compensation times.

An alternative solution, that also uses maximum detectors in the feedback loop to extract the output referred offset voltage, was proposed by Tanabe et al [12]. However, this design was implemented in a CMOS process. Compensation is performed by feeding the difference between the instantaneous maximum value of the two differential data signals to the input stage. Assuming a 50% duty cycle between high and low data transitions (i.e. the average value of the data is zero) and that the bandwidth of the maximum detector is sufficiently low, this implementation works as intended. However, this design suffers from the same limitations as previous approaches. Specifically, the data dependence of the control signal is directly related to the bandwidth of the compensation loop. When the data has extended periods with a non-zero mean value the control signal is data dependent. To minimize the data dependence of the control signal, the bandwidth of the maximum detector must be very low which leads to long compensation times.

All of the offset compensation designs considered above suffer from the same limitation. Namely, the magnitude of the output jitter is directly coupled to the offset compensation time. To reduce the output jitter in these designs the compensation loop bandwidth must be very low. This restriction results in long compensation times. The following section introduces the proposed approach which dramatically reduces the dependence of the output jitter on compensation time.

### **1.4** Proposed Approach and Contribution

There are two significant obstacles to designing a fast offset compensation network in CMOS. First accurately measuring the offset voltage of the system is difficult. The biggest reason for this is that CMOS transistors used to perform diode functions (i.e. source follower) have limited high frequency capability. Additionally, mismatches between the minimum (min) and maximum (max) detectors introduce error into the measurement. Second, it is difficult to simultaneously generate a control signal that is independent of the data while achieving fast settling performance. The reason for the difficulty is that the amount of droop at the output of the peak detector is proportional to the loop bandwidth in typical min/max detector designs.

The key contribution of this thesis is the development of a peak detector that enables the design of a fast offset compensation loop in CMOS processes that also meets strict jitter specifications. In traditional CMOS peak detectors the bandwidth is proportional to the bias current when the input is high. Similarly, when the input is low the amount of droop at the output is also proportional to  $I_{bias}$ . In the proposed peak detector this restriction has been practically eliminated. The bandwidth is still proportional to the bias current. However, the amount of droop at the output is now proportional to an NMOS transistor off-state leakage current. Since the offstate leakage current of modern CMOS devices is typically orders of magnitude less than the peak detector bias current, the amount of droop is also reduced by several orders of magnitude. This thesis focuses on the peak detector design and system implementation details.

Output jitter and settling time performance for typical offset compensation designs are compared to the targeted performance of the proposed approach in Table 1.1. Although the output jitter targets are identical, the settling time goal in the proposed solution is almost 3 orders of magnitude shorter than the typical design goals. The peak detector allows the proposed system to meet both the jitter and the aggressive settling time performance goals.

|               | Typical             | Proposed      |

|---------------|---------------------|---------------|

| Specification | Design              | Design        |

| Output Jitter | $< 2pS_{p-p}$       | $< 2pS_{p-p}$ |

| Settling Time | $\approx 500 \mu S$ | $< 1\mu S$    |

Table 1.1: Typical vs Goal Performance Specifications for Offset Compensation

## 1.5 Thesis Organization

This thesis is organized as follows. Chapter 2 introduces the proposed architecture to achieve the sub- $1\mu S$  offset compensation time while still satisfying the output jitter

requirement of the CDR input. Chapter 3 discusses the linear modeling of the proposed system architecture and computes the system parameters required to guarantee stability and the desired dynamic response. Chapter 4 presents a novel, closed-form numerical methodology for designing resistively loaded, high-speed, differential amplifiers that make up the limit amplifier. Circuit design issues and CppSim and Hspice simulation details are discussed in Chapters 5 and 6, respectively. Important layout issues are discussed in Chapter 7. Finally, Chapter 8 presents conclusions and potential extensions for future work.

## Chapter 2

## **Proposed Approach**

## 2.1 Measuring Offset Voltage

The most significant obstacles to designing a fast offset compensation network are accurately measuring the offset voltage of the system and generating a control signal that is independent of the data. This chapter incrementally develops the proposed design of the key enabling component in the offset compensation loop, the peak detector.

#### 2.1.1 Extracting the Offset Voltage with Min/Max Detectors

One possible solution for measuring the offset voltage of the limit amplifier is to take the difference between the common-mode voltages of each output signal [13]. The output common-mode level can be obtained by taking the average of the instantaneous maximum and minimum output values with max and min detectors, respectively, as shown in Figure 2-1. The max and min detectors can be either continuous time or sampled systems. Although high performance peak detectors have been designed in BiCMOS and Bipolar processes [14, 15, 16], it is not trivial to do so in CMOS processes. The fundamental design challenge is the limited high-frequency performance of CMOS transistors used to perform diode functions (i.e. source follower).

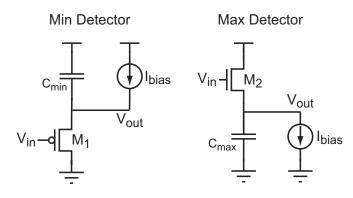

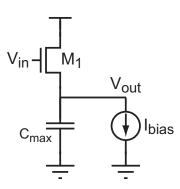

Typical maximum and minimum detector implementations are shown in Figure 2-2. The output of the minimum detector will track its input, plus a  $V_{GS}$  shift equal to  $(V_{TH}+V_{DSAT})_{M1}$ . Similarly, the output of the maximum detector will track its input, less a  $V_{GS}$  shift equal to  $(V_{TH}+V_{DSAT})_{M2}$ . In steady-state operation, both M1 and M2 remain on and either sink or source a current equal to  $I_{bias}$  such that the charge stored on  $C_{min}$  and  $C_{max}$  remains unchanged. If the output referred offset voltage increases  $I_{D,M1}$  will decrease in order to cancel charge on  $C_{min}$ .  $V_{out}$  will increase until steady state conditions are met. Likewise,  $I_{D,M2}$  will increase to add charge to  $C_{max}$  until steady state conditions are met. Conversely, if the output referred offset voltage decreases then  $I_{D,M1}$  will increase and  $I_{D,M2}$  will decrease until steady-state conditions are once again met.

Figure 2-1: Measuring Output Referred Offset Voltage Using Minimum and Maximum Detectors

Figure 2-2: Traditional Implementations for Minimum and Maximum Detectors

#### 2.1.2 Issues with Sensing Offset with Min/Max Detectors

There are two main issues with measuring the offset voltage with the different types of detectors, as shown in Figure 2-2. First, since we are attempting to measure the offset with min and max detectors that are based on PMOS and NMOS transistors, respectively, the accuracy of the measured offset is limited to the matching between the two device types. The transistor threshold voltages, transconductance and even physical dimensions will change with process, voltage and temperature variations and these changes will not necessarily track in the two devices. Ultimately, these differences will introduce offsets into the compensation loop and limit the effectiveness of the compensation.

To understand the second issue, we need to examine the max and min detectors' ability to track changes at their inputs. We will only consider the response of the max detector, here to referred to as a peak detector, and infer the min detector operation by extension.

For a unit change at the input, the output will follow by either adding charge to or subtracting charge from  $C_{max}$ . Consider first a step increase at the input. The output voltage will increase by M1 sourcing current onto  $C_{max}$  and the rate of change at the output will be limited by M1's transconductance. The ratio of the transconductance of M1 to  $C_{max}$  corresponds to the bandwidth of the peak detector while the device is

$$f_{3dB} = \frac{g_{m,M1}}{2\pi C_{max}}$$

(2.1)

Since  $g_m$  is proportional to the bias current, the bandwidth is also proportional to the bias current. If the bandwidth of the peak detector is much higher than the data rate then M1 will fully charge  $C_{max}$  so that the output will take on the correct value at each successive peak, thus operating as a zero order hold that samples the peaks of the input. If the bandwidth of the peak detector is set much lower than the data rate, the high frequency components of the input will be greatly attenuated and the output will track the lower frequency components of the input.

Alternately, consider a step decrease in the magnitude of the input signal. The output will slew according to the tail current source's ability to strip charge away from  $C_{max}$  and the change in the output voltage will be:

$$\delta V = \frac{I_{bias} - I_{M1}}{C_{max}} \cdot \delta t = \Delta \tag{2.2}$$

where  $\delta t$  is the data symbol period. The magnitude of the droop at the output is proportional to the bias current and the number of symbol periods that the input is low.

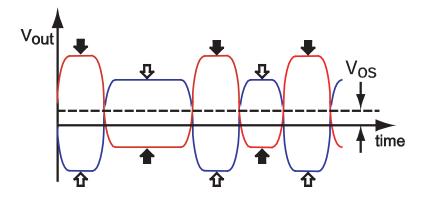

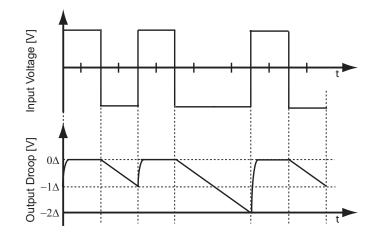

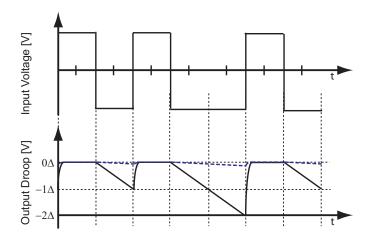

To understand why the asymmetric response of the peak detector is an issue, consider the case when the input is driven by a constant amplitude, Non-Return to Zero (NRZ), pseudo-random data stream whose amplitude does not change. Let us also assume that the peak detector operates in steady-state (i.e. the offset compensation has been performed), as shown in the top of Figure 2-3. When the input is high, the output of the peak detector will be refreshed to its correct value. However, when the input goes low,  $V_{GS,M1}$  will be reduced so  $I_{D,M1}$  will be either very low or zero and  $C_{max}$  will discharge according to Equation 2.2 as shown in the bottom of Figure 2-3. If the output is low for n symbol periods, then  $C_{max}$  will discharge according to:

$$\delta V = \frac{I_{bias}}{C_{max}} \cdot n\delta t = n \Delta \tag{2.3}$$

where and n is the number of successive low bits at the input. The total droop is defined as  $n \cdot \Delta$ . When the input goes high the output will return to the correct, steady-state value. Therefore, the measured offset voltage is data dependent and violates one of our design requirements for the offset compensation.

#### 2.1.3 Extracting Offset with Simple Max Detectors

The offset issue due to the mismatch between the NMOS and PMOS devices in the max and min detectors can be solved by taking advantage of the symmetry of the limit

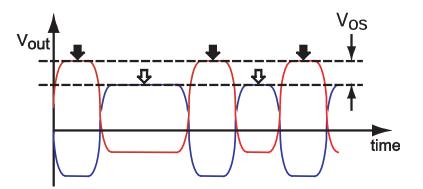

Figure 2-3: Influence of Symbol Period on Droop of Simple Peak Detector

amplifier structure. Since the data paths through the limit amplifier are differential and the amplifier stages are symmetric, the gains through each path are close to being equal, in practice. If the gains through each path are similar then the peak-to-peak values must also be equal. With zero offset in the limit amplifier, the peak values of the two paths must also be equal. However, as shown in Figure 2-4, if the output referred offset is non-zero then the peak values of two outputs will be different. In fact, the difference will equal the output referred offset and the max/min pair can be replaced by a simple peak detector, as shown in Figure 2-5. This observation eliminates the offset issue due to the mismatched min/max detectors [12].

Figure 2-4: Measuring Output Referred Offset Voltage Using Maximum Detectors Only

#### 2.1.4 Issues with Sensing Output Referred Offset with Max Detectors

The offset issue caused by mismatches between different type detectors has been solved by taking advantage of the symmetry of the limit amplifier stages. However, the basic architecture of the peak detector has not changed and it still suffers from Max Detector

Figure 2-5: Schematic of Typical CMOS Maximum Detector

the same data dependence issue described in Section 2.1.2. To solve fix this issue we need to develop a new peak detector design.

#### 2.1.5 Final Peak Detector Design

The operation of the basic peak detector was described in Section 2.1.2. The remaining issue is related to the droop of the peak detector output when the input voltage goes low. The absolute magnitude of the droop is not specifically the issue, rather the dependence of the degree of droop on the symbol period, and hence the data dependent control signal, is the issue.

The fundamental problem is that both the bandwidth of the peak detector when the input is high and the amount that the sampling capacitor is discharged when the input is low are proportional to  $I_{bias}$ . One possible solution is to decrease  $I_{bias}$ , effectively reducing the rate that charge is stripped from the storage capacitor and reducing the amount that the output droops each data period. However, since the bandwidth of the peak detector is also proportional to  $I_{bias}$  when the input is high, this approach will directly impact the tracking ability of the peak detector. We need to develop a method of measuring the offset that preserves the required slew rate and bandwidth during the tracking phase while reducing the discharge current on the hold phase. Fundamentally, there is no way to reduce the dependence of the amount of droop on the symbol period with the current topology without paying a severe performance penalty.

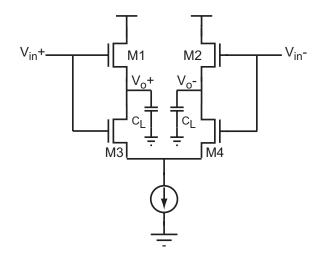

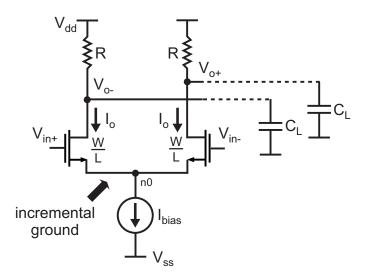

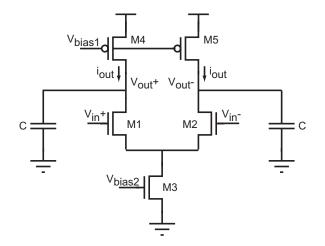

We propose that the peak detector circuit shown in Figure 2-6 provides a simple solution to this problem. Let's consider the operation of the circuit. Transistors M1 and M2 act as simple source followers, similar to device M1 in the basic peak detector described in Figure 2-5 and transistors M3 and M4 act as switches. When the input is high M3 and M4 are closed so that the peak detector behaves as a traditional peak detector. Alternately, when the input is low the switch devices are open and prevent  $I_{bias}$  from discharging  $C_{max}$ .

Compared to traditional peak detector designs, the droop in this design is greatly reduced because the switch devices, M3 and M4, dramatically reduce the dependence

Figure 2-6: Schematic of Proposed Peak Detector with Reduced Droop

of droop on  $I_{bias}$ . The amount of droop per data period in the traditional peak detector design is determined by  $I_{bias}$  while the amount of droop per data period in the proposed peak detector design is determined by the off-state current of the switch devices. Although the output of the peak detector is still dependent on the symbol length, the magnitude of the variation is greatly attenuated. This point is illustrated in Figure 2-7 by the difference in droop between the response of the traditional peak detector, represented by the solid black line, and the response of the new peak detector design, represented by the dashed line.

Figure 2-7: Comparison of Influence of Symbol Period on Droop of Simple Peak Detector vs Proposed Peak Detector Design

## 2.2 Summary

This chapter presented the design of the proposed peak detector implementation. The addition of series switch devices, which are controlled by the input, prevent the peak

detector bias current from discharging the sampling capacitor when the peak detector input is low. In traditional peak detector designs both the peak detector bandwidth and droop are determined by the peak detector bias current. In the proposed design the bandwidth of the peak detector is determined by its bias current while the droop is determined by transistor off-state leakage current. By substantially reducing the dependence of the droop on the bias current, this peak detector design enables the system to simultaneously achieve the fast settling time and low output jitter goals. In the next chapter the system modeling issues will be discussed.

# Chapter 3

# System Modeling

The peak detector design presented in the previous chapter is the corner-stone of the offset compensation loop. The system topology and modeling of each control loop will be presented in this chapter. Additionally, we will determine the system parameters that provide the desired system dynamics in this chapter. There are several performance parameters that must be considered when determining the system parameters:

- Loop bandwidth → compensation time: Determined by compensation time goal and impact on jitter of output signal.

- Forward path gain: Based on input and output signal characteristics

- Output jitter: Need to minimize output jitter for the CDR that follows

- System stability: Unconditional requirement

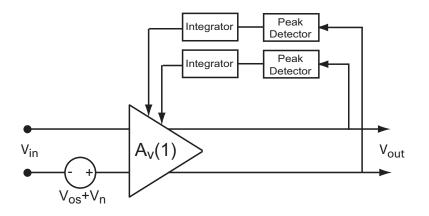

### 3.1 System Level Implementation

The next step is to pull all of the pieces together and implement the complete control loop. A fully differential implementation of the system is shown in Figure 3-1. The peak detector is used to measure the offset referred to the output of the limit amplifier. The integrator in the feedback path filters the instantaneous peak detector output. Additionally, the integrator forces the steady-state, output-referred offset voltage to be zero regardless of the loop gain. However, there are a few changes that need to be made to the system based on the assumptions that we made in developing the proposed peak detector design.

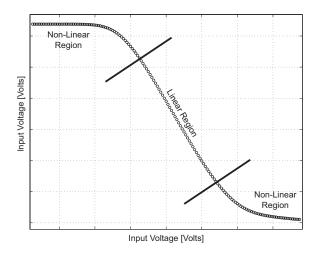

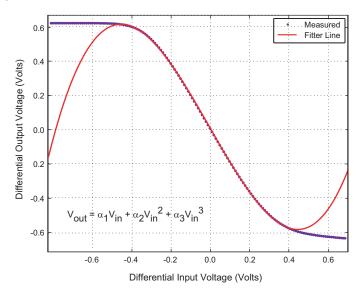

As explained in Section 2.1.3, the offset information is contained in the peaks of the outputs (i.e. the output referred offset is equal to the difference in the peak values). Therefore, we need to account for the case when the output of the limit amplifier becomes saturated. A typical DC transfer function between the input voltage and output voltage of the basic limit amplifier stage is shown in Figure 3-2. The output nonlinearly approaches a maximum value, determined by the positive power supply, and ultimately saturates due to either a large input amplitude or a large offset.

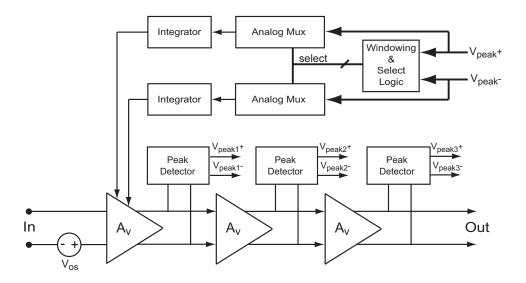

Figure 3-1: System Level of Limit Amplifier with Offset Compensation

Compensation will be ineffective, or at least severely degraded in performance, if we attempt to measure the offset from the saturated output. To solve this problem, multiple control loops are used with taps located at each of the limit amplifier stage outputs, as shown if Figure 3-3. The windowing and select logic determines the first amplifier stage with a non-saturated output and compensates the output referred offset at the selected output. Additionally, the select logic is dynamic and the selected output tap location can change as the system is compensated and outputs later in the amplifier chain become unsaturated.

Figure 3-2: Typical Transfer Function for Limit Amplifier Cell

As shown in Figure 3-2, for large amplitude inputs the output nonlinearly approaches the maximum value defined by the positive power supply. This nonlinearity can also reduce the effective gain of the offset compensation loop. To minimize this undesired effect, the switching threshold of the windowing logic can be set lower than the positive supply voltage, say by 50 - 100mV, so that the non-linear portion of the amplifier transfer function does not impact the offset compensation. There are two seeming drawbacks to this solution.

First, the maximum amplitude of input referred offset that the system can compen-

Figure 3-3: Complete System Showing Multiple Control Loops and Logic

sate is reduced because we have limited the range of each loop to avoid the non-linear portion of the amplifier transfer function. However, the input referred offset would have to be large enough to saturate the output of the first stage in the limit amplifier for this to become an issue. In this design, the maximum input referred offset that can be compensated is 450mV. However, it is highly unlikely that the input referred offset would be this large.

The second potential issue is that the amplifier cells situated after the selected compensation tap in the limit amplifier operate open-loop and any offset added by these stages will not be compensated. As mentioned in Chapter 1, the DC offset introduced by each limit amplifier stage, referred to its own input, will be on the order of a few millivolts. Each of these offset components are referred to the output of the limit amplifier through the gain of subsequent stages. The aggregate output referred offset that can not be compensated is the sum of these components. Assuming that the total output referred offset remains on the order of a few 10's of millivolts, which will be true in practice, this condition is acceptable. The goal of the offset compensation is to eliminate the gross offset that causes the output of any stage in the limit amplifier to saturate.

To ensure that the system dynamics are consistent over all possible offset values, the system parameters for each control loop are set equal. Since the gain increases at each subsequent output of the limit amplifier, the gain in each feedback path must be adjusted to satisfy this requirement. Full details of the system modeling will be covered later in this chapter.

# 3.2 Linear System Modeling

To model the control loop we need to make some simplifying assumptions. First, to eliminate the difficulty of analyzing multiple control loops, we only consider the case when there is one active control loop. In the end, we can extend the analysis to the more general case when there are multiple control loops and test that this assumption is valid in simulation. Further, we can assume that all blocks in the system are linear about a given operating point and make use of LTI modeling techniques. We will now develop models for each of the system blocks.

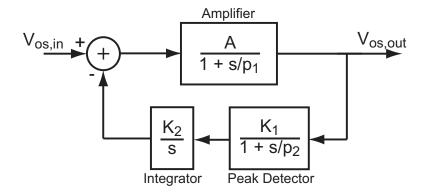

Each of the amplifiers in the forward amplifier path can be modeled by a DC gain and a single pole, representing the bandwidth of the amplifier. Therefore, the linear model for each amplifier is:

$$H(s) = \frac{A_v}{1 + s/p_1}$$

(3.1)

where  $A_v$  is the gain and  $p_1$  is the pole at the 3dB frequency. If we consider a cascade of n amplifiers, the aggregate transfer function becomes:

$$H(s) = \left(\frac{A_v}{1 + s/p_1}\right)^n \tag{3.2}$$

Additionally, the peak detector can be similarly modeled by its DC gain,  $K_1$ , and a single pole,  $p_2$ , and has the same form as Equation 3.1. If the bandwidth of the peak detector is low enough the model takes the same form as Equation 2.1 after some simplification. The justification for this abstraction is that the peak detector only needs to measure the average output referred offset of the system, or the DC component of the output signal. To first order, the output of the peak detector is not affected by instantaneous variations at its input. The final form of the peak detector model is:

$$H(s) = \frac{K_1}{1 + s/p_2} = \frac{K_1 \cdot p_2}{s}$$

(3.3)

The integrator can be modeled as an ideal integrator:

$$H(s) = \frac{K_2}{s} \tag{3.4}$$

where  $K_2$  is the gain. Putting all of the pieces together, the complete model for the forward amplifier path and the offset compensation is shown in Figure 3-4.

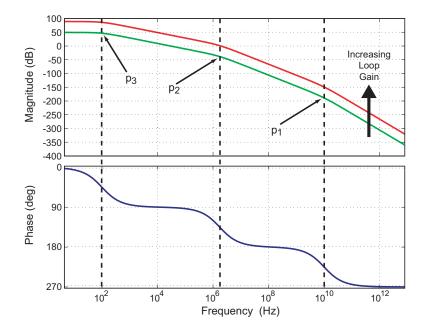

For the following discussion, we assume that  $p_1 \gg p_2$ . This is valid in this system since  $p_1$  corresponds to the bandwidth of the limit amplifier (10GHz), and  $p_2$  corresponds to the bandwidth of the peak detector ( $\approx 10$ MHz). In a similar fashion to the linear model for a PLL, where the state variable is phase and not the data signal itself, the variable of interest in this system is the offset voltage. To characterize the system response, we define the open loop response to be:

Figure 3-4: Linear Model of Limit Amplifier with Offset Compensation

$$A(s) = \left(\frac{A_v}{1 + s/p_1}\right) \left(\frac{K_1}{1 + s/p_2}\right) \left(\frac{K_2}{s}\right)$$

(3.5)

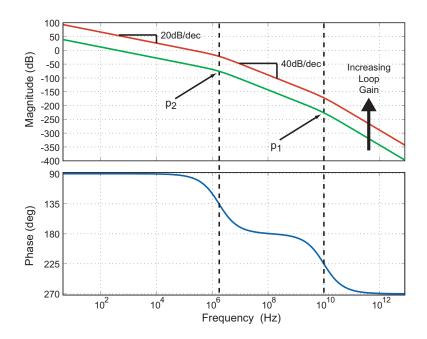

The necessary criteria for stability can be determined based on traditional feedback heuristics by analyzing the behavior of the open-loop parameter A(s). In this system,  $p_2$  is the peak detector pole location and  $f_u$  is the unity-gain frequency. From the Bode plot in Figure 3-5, we can readily see that the integrator in the feedback path reduces the magnitude at 20dB/dec at frequencies below the first pole,  $p_2$ , and introduces a 90° phase shift. Phase margin is defined as the difference in phase from 180° at unity gain. If we require greater than 45° of phase margin to be stable then a necessary condition is that  $p_2 \ge f_u$ . Additionally, as the loop gain increases, the unity-gain frequency increases and the phase margin, and therefore stability, degrades. Ultimately, there are optimal values for  $p_2$  and the loop gain,  $A_v K_1 K_2$ , that guarantee stability and provide the desired loop dynamics.

To gain more intuition of the system modeling, we can further define a closed loop response parameterizing function G(s) as:

$$G(s) = \frac{A(s)}{1 + A(s)} \tag{3.6}$$

where A(s) is the open loop response defined above. If  $AK_1K_2 = 0$  then the loop is open, there is one closed-loop pole,  $p_{1,closed-loop}$ , located at the origin and there is a pair of closed-loop poles located at:

$$p_{2/3,closed-loop} = -0.5 \cdot \left[ (p_1 + p_2) \mp \sqrt{(p_1 + p_2)^2 - 4p_1 p_2} \right]$$

(3.7)

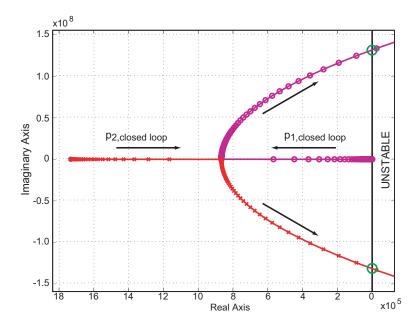

The pole locations,  $p_{2/3,closed-loop}$ , roughly correspond to the open-loop pole locations,  $p_1$  and  $p_2$ . To understand how the closed-loop poles vary with increased gain, we construct the root locus plot in Figure 3-6. As the DC loop gain increases, the first

Figure 3-5: Bode Plot Showing Stability Degradation with Increasing Gain

two closed-loop poles,  $p_{1,closed-loop}$  and  $p_{2,closed-loop}$ , approach each other from zero and the first open-loop pole location  $(p_2)$  along the negative real axis as shown in Figure 3-6. Additionally,  $p_{3,closed-loop}$  moves away from the origin along the negative real axis. When  $AK_1K_2 \approx p_2/4$ , where  $p_2$  is the second open-loop pole corresponding to the peak detector, a complex conjugate pole pair is formed that diverges at an angle of  $\pm 60^{\circ}$  to the real axis. As the open-loop gain increases, the poles will cross into the right-half-plane and the system will become unstable. So, how do we determine the value of gain that not only guarantees stability but also provides the desired settling response? One solution is to use the PLL Design Assistant [17].

#### 3.2.1 Modeling System Response with PLL Design Assistant

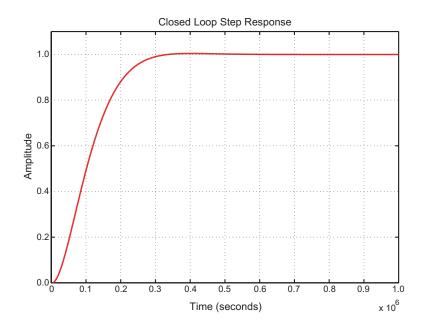

The PLL Design Assistant is a useful tool that was developed to aid the design of PLL systems and can be downloaded at http://www-mtl.mit.edu/perrottgroup/tools.html. However, with a little imagination this tool can be used to model nearly any linear system. We can think of the system in Figure 3-4 as a second order, type I PLL with the forward amplifier path corresponding to a high frequency parasitic pole. Let's assume that the open-loop pole  $p_1$  is set to 10GHz, based on the desired data-rate, and that the gain of the peak detector,  $K_1$ , is unity. Then, using the PLL Design Assistant we can specify a desired closed-loop bandwidth, based on the desired compensation settling time, and step-response shape to achieve the optimal settling time.

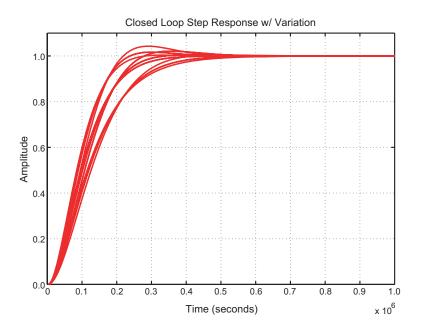

For example, Figure 3-7 illustrates the GUI of the PLL Design Assistant designing the system loop with a Bessel shape and a bandwidth of 2.5MHz. The resulting gain coefficient, K, corresponds to the product  $A_v K_2$ , assuming that the peak detector has a gain of one. The pole frequency,  $f_p$ , corresponds to the open-loop

Figure 3-6: Root Locus Plot of G(s) Showing Necessary Condition for Stability

pole of the peak detector,  $p_2$ . Note that the closed-loop complex conjugate pole pair follow the trajectory determined in the root locus analysis and that the frequency of the open-loop pole  $p_2$  is higher than the dominant closed-loop pole frequency, as required by our earlier stability analysis. The resulting step-response of the closedloop system, shown in Figure 3-8, indicates that the total settling time for the offset compensation is roughly 500nS and that the system is stable.

| PLL Design Assistant     File Edit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |                      |                            |                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dynamic Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | paris. pole 10e9                                                                                | Hz                   | On                         | Noise Parameters                                                                                                                                                                                                                                                   |  |  |  |

| fo         2.5e6         Hz           order         C 1         0.2         3           shape         C Butter         C Bessel         C Cheby1           C Cheby1         C Cheby2         C Elliptical           ripple         dB           type         0.1         C.2           type         1         C.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | paris. Q<br>paris. pole<br>paris. Q<br>paris. pole<br>paris. pole<br>paris. zero<br>paris. zero | Hz<br>Hz<br>Hz<br>Hz | On<br>On<br>On<br>On<br>On | ref. freq         Value?         Hz           out freq.         Value?         Hz           Detector         dBc/Hz         On           VCO         dBc/Hz         On           freq. offset         Hz         S-D           C 1         2         On         On |  |  |  |